# 256-BIT BIPOLAR RAM (256x1 RAM) (82S116 TRI-STATE) (82S117 OPEN COLLECTOR) 82S117

## FEBRUARY 1975 DIGITAL 8000 SERIES TTL/MEMORY

#### DESCRIPTION

The 82S116 and 82S117 are Schottky clamped TTL, read/write memory arrays organized as 256 words of one bit each. They feature either open collector or tri-state output options for optimization of word expansion in bussed organizations. Memory expansion is further enhanced by full on-chip address decoding, 3 chip enable inputs and PNP input transistors which reduce input loading to  $25\mu$ A for a "1" level, and –  $100\mu$ A for a "0" level.

During WRITE operation, the logical state of the output of both devices follows the complement of the data input being written. This feature allows faster execution of WRITE-READ cycles, enhancing the performance of systems utilizing indirect addressing modes, and/or requiring immediate verification following a WRITE cycle.

Both devices have fast read access and write cycle times, and thus are ideally suited in high-speed memory applications such as "Cache", buffers, scratch pads, writable control stores, etc.

Both 82S116 and 82S117 devices are available in the commercial temperature range. For the commercial temperature range,  $(0^{\circ}C \text{ to } +75^{\circ}C)$  specify N82S116/117, B or F.

#### **FEATURES**

- ORGANIZATION 256 X 1

- ADDRESS ACCESS TIME 40ns, MAXIMUM

- WRITE CYCLE TIME 25ns, MAXIMUM

- POWER DISSIPATION 1.5mW/BIT TYPICAL

- INPUT LOADING (-100 $\mu$ A) MAXIMUM

- OUTPUT FOLLOWS COMPLEMENT OF DATA INPUT DURING WRITE

- ON-CHIP ADDRESS DECODING

- OUTPUT OPTION: TRI-STATE – 82S116 OPEN COLLECTOR – 82S117

- 16 PIN CERAMIC DIP

#### APPLICATIONS

BUFFER MEMORY WRITABLE CONTROL STORE MEMORY MAPPING PUSH DOWN STACK SCRATCH PAD

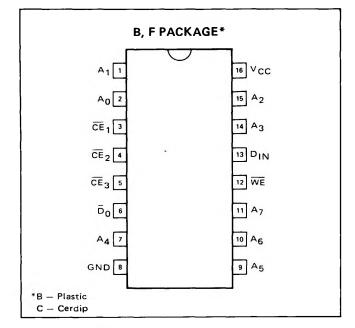

## **PIN CONFIGURATION**

#### **TRUTH TABLE**

|           |     |    |     | DOUT           |                |  |  |

|-----------|-----|----|-----|----------------|----------------|--|--|

| MODE      | CE* | WE | DIN | 82S116         | 82\$117        |  |  |

| READ      | 0   | 1  | х   | STORED<br>DATA | STORED<br>DATA |  |  |

| WRITE "0" | 0   | 0  | 0   | 1              | 1              |  |  |

| WRITE "1" | 0   | 0  | 1   | 0              | 0              |  |  |

| DISABLED  | 1   | X  | X   | High-Z         | 1              |  |  |

\*''0" = All CE inputs low; "1" = one or more CE inputs high. X = Don't care.

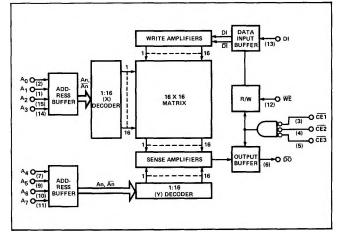

#### **BLOCK DIAGRAM**

#### **ABSOLUTE MAXIMUM RATINGS**

|                    | PARAMETER                          | RATING                          | UNIT |

|--------------------|------------------------------------|---------------------------------|------|

| V <sub>CC</sub>    | Power Supply Voltage               | +7                              | Vdc  |

| V <sub>IN</sub>    | Input Voltage                      | +5.5                            | Vdc  |

| Vout               | High Level Output Voltage (82S117) | +5.5                            | Vdc  |

| vo                 | Off-State Output Voltage (82S116)  | +5.5                            | Vdc  |

| <br>Τ <sub>Α</sub> | Operating Temperature Range        | $0^{\circ}$ to +75 $^{\circ}$   | °C   |

| T <sub>stg</sub>   | Storage Temperature Range          | $-65^{\circ}$ to $+150^{\circ}$ | °C   |

## **ELECTRICAL CHARACTERISTICS** $0^{\circ}C \leq T_{A} \leq 75^{\circ}C$ , 4.75V $\leq V_{CC} \leq 5.25V$

| PARAMETER       |                                            |                                                    | LIMITS |                  |      |      |       |

|-----------------|--------------------------------------------|----------------------------------------------------|--------|------------------|------|------|-------|

|                 |                                            | TEST CONDITIONS                                    | MIN    | TYP <sup>2</sup> | MAX  | UNIT | NOTES |

| V <sub>IH</sub> | High-Level Input Voltage                   | V <sub>CC</sub> = 5.25V                            | 2.0    |                  |      | v    |       |

| VIL             | Low-Level Input Voltage                    | V <sub>CC</sub> = 4.75V                            |        |                  | 0.85 | v    | 1     |

| VIC             | Input Clamp Voltage                        | V <sub>CC</sub> = 4.75V, I <sub>IN</sub> = -12 mA  |        | -1.0             | -1.5 | v    | 1,8   |

| V <sub>OH</sub> | High-Level Output Voltage (82S116)         | V <sub>CC</sub> = 4.75V, I <sub>OH</sub> = -3.2 mA | 2.6    |                  |      | V    | 1,6   |

| VOL             | Low-Level Output Voltage                   | V <sub>CC</sub> = 4.75V, I <sub>OL</sub> = 16 mA   |        | 0.35             | 0.45 | V    | 1,7   |

| IOLK            | Output Leakage Current<br>(82S117)         | V <sub>OUT</sub> = 5.5V                            |        | 1                | 40   | μΑ   | 5     |

| IO(OFF)         | HI-Z State Output Current                  | V <sub>OUT</sub> = 5.5V                            |        | 1                | 40   | μΑ   | 5     |

|                 | (82S116)                                   | V <sub>OUT</sub> = 0.45V                           |        | -1               | -40  | μΑ   | 5     |

| I <sub>IH</sub> | High-Level Input Current                   | V <sub>CC</sub> = 5.25V, V <sub>IN</sub> = 5.5V    |        | 1                | 25   | μΑ   | 8     |

| կլ              | Low-Level Input Current                    | V <sub>CC</sub> = 5.25V, V <sub>IN</sub> = 0.45V   |        | -10              | -100 | μΑ   | 8     |

| I <sub>OS</sub> | Short-Circuit Output Current (82S116)      | V <sub>CC</sub> = 5.25V, V <sub>O</sub> = 0V       | -20    |                  | -70  | mA   | 3     |

| I <sub>CC</sub> | V <sub>CC</sub> Supply Current<br>(82S116) | V <sub>CC</sub> = 5.25V                            |        | 80               | 115  | mA   | 4     |

|                 | V <sub>CC</sub> Supply Current<br>(82S117) | V <sub>CC</sub> = 5.25V                            |        | 80               | 115  | mA   | 4     |

| CIN             | Input Capacitance                          | $V_{IN} = 2.0V$                                    |        | 5                |      | pF   |       |

| COUT            | Output Capacitance                         | $V_{OUT} = 2.0V$ $V_{CC} = 5.0V$                   |        | 8                |      | pF   |       |

NOTES:

1. All voltage values are with respect to network ground terminal.

2. All typical values are at  $V_{CC} = 5V$ ,  $T_A = +25^{\circ}C$ .

3. Duration of the short-circuit should not exceed one second.

4. I<sub>CC</sub> is measured with the write enable and memory enable inputs grounded, all other inputs at 4.5V, and the output open.

5. Measured with  $V_{IH}$  applied to CE1, CE2 and CE3.

6. Measured with a logic "0" stored and V<sub>1L</sub> applied to  $\overline{CE_1}$ ,  $\overline{CE_2}$  and  $\overline{CE_3}$ .

7. Measured with a logic "1" stored. Output sink current is supplied through a resistor to  $V_{CC}$ .

8. Test each input one at the time.

#### SIGNETICS 256-BIT BIPOLAR RAM (256 X 1 RAM) = 82S116, 82S117

## SWITCHING CHARACTERISTICS $0^{\circ}C \leq T_{A} \leq +75^{\circ}C$ , 4.75V $\leq V_{CC} \leq 5.25V$

| PARAMETER        |                                     | TEST CONDITIONS       | LIMITS |                  |     |      | 1075   |

|------------------|-------------------------------------|-----------------------|--------|------------------|-----|------|--------|

|                  |                                     | TEST CONDITIONS       | MIN    | TYP <sup>1</sup> | MAX | UNIT | NOTE   |

| Propaga          | ation Delays                        |                       |        |                  |     |      |        |

| T <sub>AA</sub>  | Address Access Time                 |                       |        | 30               | 40  | ns   |        |

| T <sub>CE</sub>  | Chip Enable Access Time             | $R_1 = 270\Omega$     | ţ      | 15               | 25  | ns   |        |

| т <sub>ср</sub>  | Chip Enable Output Disable Time     | $R_2 = 600\Omega$     | 1      | 15               | 25  | ns   |        |

| T <sub>WD</sub>  | Write Enable to Output Disable Time | C <sub>L</sub> = 30pF |        | 30               | 40  | ns   | i<br>I |

| Write S          | et-up Times                         |                       |        |                  |     |      |        |

| T <sub>WSA</sub> | Address to Write Enable             |                       | 0      | -5               |     | ns   |        |

| T <sub>WSD</sub> | Data In to Write Enable             |                       | 25     | 15               |     | ns   |        |

| T <sub>WSC</sub> | CE to Write Enable                  |                       | 0      | -5               |     | ns   |        |

| Write H          | old Times                           |                       |        | ·                |     | •    |        |

| T <sub>WHA</sub> | Address to Write Enable             |                       | 0      | -5               |     | ns   |        |

| т <sub>wнd</sub> | Data In to Write Enable             |                       | 0      | -5               |     | ns   |        |

| т <sub>wнс</sub> | CE to Write Enable                  |                       | 0      | -5               |     | ns   |        |

| T <sub>WP</sub>  | Write Enable Pulse Width            |                       | 25     | 15               |     | ns   | 2      |

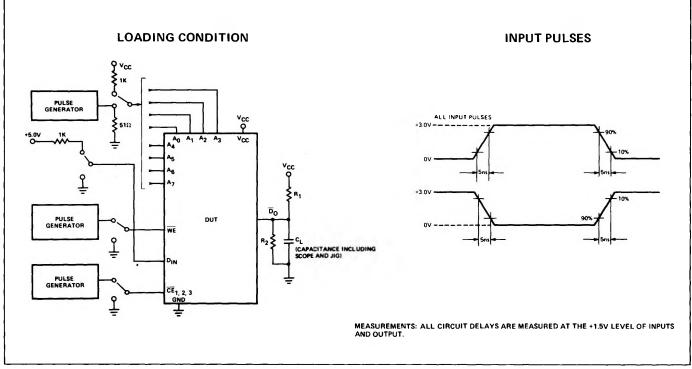

### AC TEST LOAD

NOTES:

- 1. Typical values are at V<sub>CC</sub> = +5.0V, and T<sub>A</sub> = +25 $^{\circ}$ C.

- 2. Minimum required to guarantee a WRITE into the slowest bit.

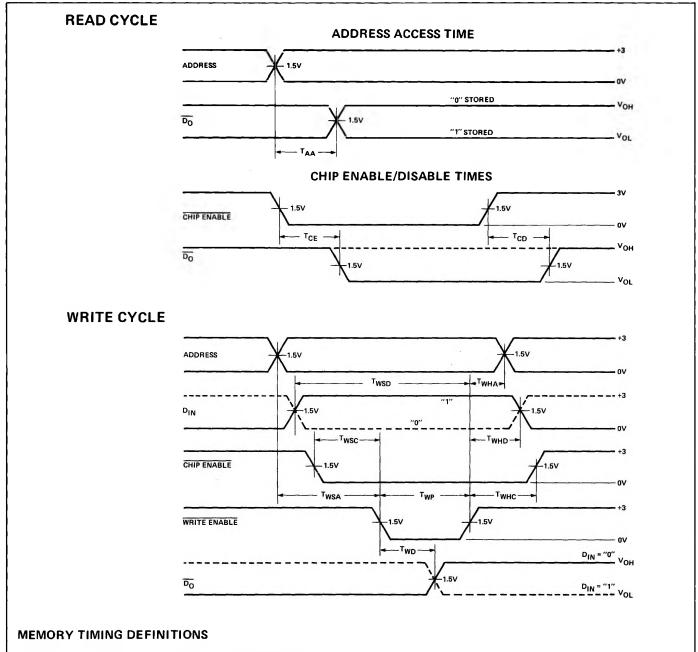

#### SWITCHING PARAMETERS MEASUREMENT INFORMATION

- T<sub>CE</sub> Delay between beginning of CHIP ENABLE low (with ADDRESS valid) and when DATA OUTPUT becomes valid.

- T<sub>CD</sub> Delay between when CHIP ENABLE becomes high and DATA OUTPUT is in off state.

- T<sub>AA</sub> Delay between beginning of valid ADDRESS (with CHIP ENABLE low) and when DATA OUTPUT becomes valid.

- T<sub>WSC</sub> Required delay between beginning of valid CHIP ENABLE and beginning of WRITE ENABLE pulse.

- T<sub>WHD</sub> Required delay between end of WRITE ENABLE pulse and end of valid INPUT DATA.

- T<sub>WP</sub> Width of WRITE ENABLE pulse.

- T<sub>WSA</sub> Required delay between beginning of valid ADD-RESS and beginning of WRITE ENABLE pulse.

- T<sub>WSD</sub> Required delay between beginning of valid DATA INPUT and end of WRITE ENABLE pulse.

- T<sub>WD</sub> Delay between beginning of WRITE ENABLE pulse and when DATA OUTPUT reflects complement of DATA INPUT.

- T<sub>WHC</sub> Required delay between end of WRITE ENABLE pulse and end of CHIP ENABLE.

- T<sub>WHA</sub> Required delay between end of WRITE ENABLE pulse and end of valid ADDRESS.