# 8220

## PRODUCT AVAILABLE IN 0°C TO 75°C TEMPERATURE ONLY

## DESCRIPTION

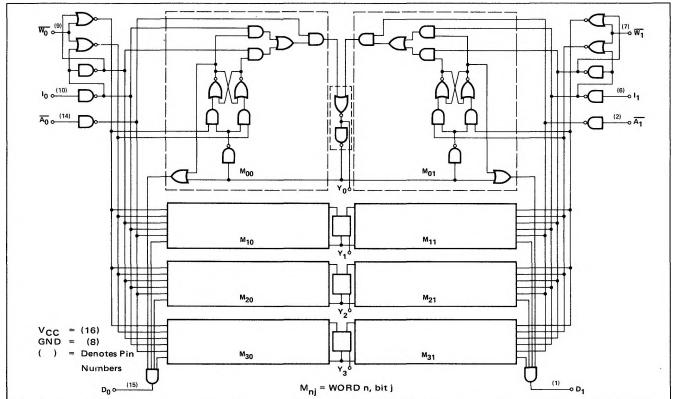

The 8220 CAM Element is a high speed monolithic array, incorporating the necessary addressing logic and eight identical memory cells organized as four words, each being two bits long. In reference to data-in/data-stored, the 8220 can be conditioned to perform the following functions: associate, write-in only, and read-out only.

When addressed into the "ASSOCIATE" mode, this element offers the novel capability of data association, where each cell  $(M_{nj})$  will respond with a "Match" or "Mismatch" answer  $(Y_{n})$  to each bit presented to the data inputs  $(I_{j})$ , depending on presence or absence of an alike bit stored within the cell.

Write-in can be simultaneously done to all bits, or one bit at a time. Read-out of stored information is performed on

one word at a time. Cell-selection for read and write is performed by proper addressing of  $Y_{\rm h}$  and  $A_{\rm h}$  lines.

The element's output structures  $(Y_n \text{ and } D_j)$  are of the "bare collector" variety and can be mutually connected, thus allowing direct expansion when multiple packages are employed. Expansion of the CAM may be implemented in

# DIGITAL 8000 SERIES TTL/MSI

both directions, i.e., in the word length and in the number of words.

The CAM circuit structure is the familiar TTL type (DCL Family) and fully compatible with TTL and DTL input/ output structures.

## FEATURES

- WRITE ENABLE CONTROL LINES

- ASSOCIATE CONTROL LINES

- ADDRESS SELECT CONTROL LINES

- ASSOCIATES IN 20nsec TYP.

- 16 PIN PACKAGE (1/3 SIZE OF 24 PIN PACKAGE)

- OPEN COLLECTOR OUTPUTS

- DIODE PROTECTED INPUTS

APPLICATIONS DATA-TO-MEMORY COMPARISON PATTERN RECOGNITION HIGH SPEED INFORMATION RETRIEVAL CACHE MEMORY AUTO CORRELATION VIRTUAL MEMORY LEARNING MEMORY

## LOGIC DIAGRAM

# SIGNETICS DIGITAL 8000 SERIES TTL/MSI - 8220

|                            | LIMITS |      |      |       | _    | _    |      |      |      |        |       |

|----------------------------|--------|------|------|-------|------|------|------|------|------|--------|-------|

| CHARACTERISTICS            | MIN.   | TYP. | MAX. | UNITS | Wj   | Āj   | Ij   | Yi   | Yk   | Dj     | NOTES |

| "0" Output Voltage         |        |      |      |       |      |      |      |      |      |        |       |

| Yn                         | 1      |      | 0.4  | v     | 2.0V | 0.8V | 2.0V | 30mA |      | Sec. 1 | 8,9   |

|                            |        |      | 0.6  | v     | 2.0V | 0.8V | 2.0V | 60mA |      |        |       |

| Dj                         |        |      | 0.4  | V     | 2.0V | 2.0V | -X-  |      | 0.8V | 20mA   | 8,9   |

|                            |        | à.   | 0.6  | V     | 2.0∨ | 2.0∨ |      |      | 0.8∨ | 40mA   |       |

| "1" Output Leakage Current |        |      |      |       |      |      |      |      |      |        |       |

| Yn                         |        |      | 125  | μA    |      | 2.0V |      |      |      |        | 10    |

| Dj                         | -      |      | 100  | μA    |      |      |      | 0V   | 0V   |        | 10    |

| "1" Input Current          |        |      |      |       |      |      |      |      |      |        |       |

| lj and $\overline{A_{j}}$  |        |      | 40   | μA    |      | 4.5V | 4.5V |      |      |        |       |

| Wj                         |        |      | 80   | μΑ    | 4.5V |      |      |      |      |        |       |

| "0" Input Current          |        |      |      |       |      |      |      |      |      |        |       |

| lj, Yn and Aj              | -0.1   |      | -1.2 | mA    |      | 0.4∨ | 0.4∨ | 0.4V |      |        |       |

|                            |        |      |      |       |      |      |      |      |      |        |       |

|                            |        |      |      |       |      |      |      |      |      |        | }     |

|                            |        |      |      |       |      |      |      |      |      |        |       |

|                            |        |      |      |       |      |      |      |      |      |        |       |

Ň

## ELECTRICAL CHARACTERISTICS (Over Recommended Operating Temperature And Voltage)

# $T_A = 25^{\circ}C$ and $V_{CC} = 5.0V$

|                                            | LIMITS |      |             |       |    |    |    |    |    |      |       |

|--------------------------------------------|--------|------|-------------|-------|----|----|----|----|----|------|-------|

| CHARACTERISTICS                            | MIN.   | TYP. | MAX.        | UNITS | Wj | Aj | Τj | Yi | Yk | Dj   | NOTES |

| Delay Time                                 |        |      |             |       |    |    |    |    |    |      |       |

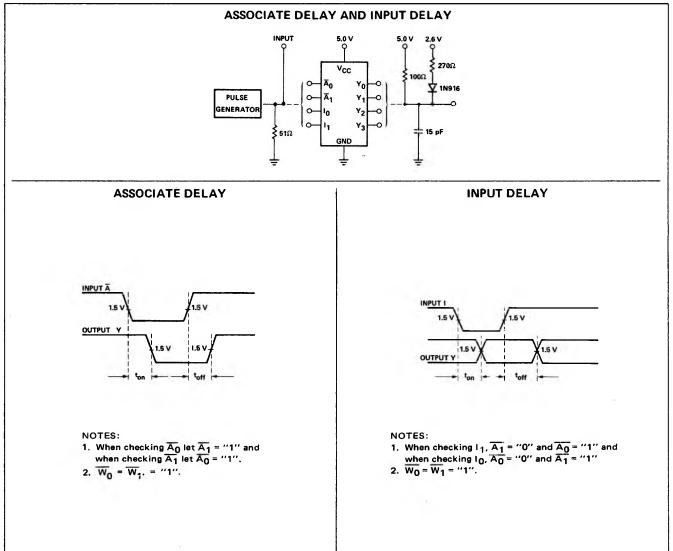

| Associate (Aj to Yn)                       |        | 20   | 30          | ns    |    |    |    |    |    | 12.1 | 8, 11 |

| Associate (lj to Yn)                       |        | 35   | 45          | ns    |    |    |    |    |    |      | 8, 11 |

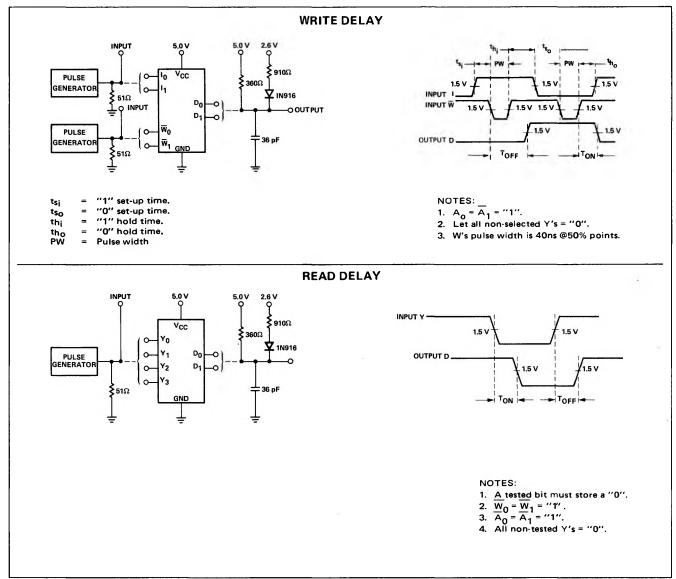

| Read-Out (Yn to Dj)                        |        | 30   | 40          | ns    |    |    |    |    |    |      | 8, 11 |

| Write-In to <u>Rea</u> d-Out<br>(Wj to Dj) |        | 45   | 60          | ns    |    |    |    |    |    |      |       |

| Write Pulse Width                          |        | 20   | 35          | ns    |    |    |    |    |    |      |       |

| Power Consumption                          |        |      | 590/<br>118 | mW/mA |    |    |    |    |    |      |       |

|                                            |        |      |             |       |    |    |    |    |    |      |       |

|                                            |        |      |             |       |    |    |    |    |    |      |       |

#### NOTES:

- All voltage and capacitance measurements are referenced to 1. the ground terminal. Terminals not specifically referenced are left electrically open.

- 2. All measurements are taken with ground pin tied to zero volts.

- З. Positive current is defined as into the terminal referenced.

- Positive NAND logic definition: "UP" Level = "1", "DOWN" 4. Level = "0".

- 5. Precautionary measures should be taken to ensure current limiting in accordance with Absolute Maximum Ratings

should the isolation diodes become forward biased.

- Measurements apply to each gate element independently. 6. Manufacturer reserves the right to make design and process 7. changes and improvements.

- 8. Prior to this test write in a "0" in all or desired Memory

- cells as follows: Wj = Ij = 0V, Aj =  $V_{CC}$ . Output sink current is supplied through a resistor to  $V_{CC}$ . Connect an external 1K ohm + 1% resistor from  $V_{CC}$  to the 9.

- 10. output terminal for this test.

- 11. See AC test Figures on the following pages.

# SIGNETICS DIGITAL 8000 SERIES TTL/MSI - 8220

## MODE OF OPERATION

| FUNCTION  | ₩ <sub>0</sub> ₩ <sub>1</sub> ឝ <sub>0</sub> ឝ <sub>1</sub> ι <sub>0</sub> ι <sub>1</sub> | REMARKS<br>(Ref. Definitions & Glossary)                                                                                                                                                                                                                                                                                           | FUNCTION | $\overline{W}_0 \overline{W}_1 \overline{A_0} \overline{A_1} I_0 I_1$ | REMARKS<br>(Ref. Definitions & Glossary)               |  |  |  |

|-----------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------------------------------------------|--------------------------------------------------------|--|--|--|

| HOLD      | 1 1 1 1 x x                                                                               | NO OPERATION                                                                                                                                                                                                                                                                                                                       | HOLD     | 1 1 1 1 x x                                                           | NO OPERATION                                           |  |  |  |

| ASSOCIATE |                                                                                           | Output<br>Question Answer State<br>?<br>$I_1=M_{i1}$<br>$-YES - Y_i=1, Y_k=0$<br>$NO - Y_i=Y_k=0$<br>?<br>$I_0=M_{i0}$<br>$-NO - Y_i=1, Y_k=0$<br>$NO - Y_i=Y_k=0$                                                                                                                                                                 | ~        | 1 0 1 1 x x<br>0 1 1 1 x x<br>0 0 1 1 x x                             |                                                        |  |  |  |

|           | 1 1 0 0 x x                                                                               | $\begin{bmatrix} \mathbf{U} & \mathbf{i} \mathbf{U} \\ \mathbf{U} & \mathbf{V} \end{bmatrix} = \mathbf{NO} = \mathbf{Y}_{i} = \mathbf{Y}_{k} = 0$ $\begin{bmatrix} \mathbf{I}_{1} = \mathbf{M}_{i1} \\ and ? \\ \mathbf{I}_{0} = \mathbf{M}_{i0} \end{bmatrix} = \mathbf{VES} = \mathbf{Y}_{i} = \mathbf{I}, \ \mathbf{Y}_{k} = 0$ | READ-OUT | 1 1 1 1 x x<br>1 1 1 1 x x<br>1 1 1 1 x x                             | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |  |  |  |

# AC TEST FIGURES AND WAVEFORMS

## SIGNETICS DIGITAL 8000 SERIES TTL/MSI - 8220

# AC TEST FIGURES AND WAVEFORMS (Cont'd)

GENERAL NOTES FOR AC TESTING:

- 1. Use 5k Probes for all AC tests TEK 169 or equivalent,

- The Pulse Generator signal should consist of the following Frequency: 10 MHz ±5 MHz Amplitude: 0V to 3V

- Rise & Fall Times: 5 ns ±2ns

- 3. i = bit number (i = 0, 1). j = word number (j = 0, 1, 2, 3).

# INPUT/OUTPUT DEFINITIONS

- Data Inputs ١

- Data entering these terminals are either compared with stored information at the cell(s) in the "associate" mode or stored in the cell(s) in the "write-in" mode. Ā<sub>i</sub> – Associate Controls

- A logical "O" at this pin enables Data-Cell association to result into a defined logical level at the Y<sub>n</sub> lines (e.g. Y<sub>n</sub> = "1" = Match, Y<sub>n</sub> = "0" Mismatch). A logical "1" at this pin forces all Y<sub>n</sub> to a "1".

- W: Write Enable A logical "O" at this control pin opens the gates of the selected word, allowing data-in to be stored. A logical "1" locks the gates such that data-in can no longer disturb the cell(s).

- "Associate" Output and Address Selection Control Y\_\_ -During "Associate" mode these "bare collector" lines provide output results of match or mismatch between input and stored

data (logical "1" = Match, logical "0" = Mismatch).

In the read and write modes these terminals act as input controls and word-select lines Y lines  $(Y_1)$  associated with words desired to accept writing of data or read-out are to be kept in the logical "1" state and the remaining Y lines  $(Y_k)$  to be forced to a logical "O" state. (Note that A = 1 forces all Y<sub>n</sub> = 1).

Α.

D<sub>j</sub> - Data Output These are "bare collector" output lines indicating the state of one or more selected cells. Cell-Selection is accomplished as defined under "Yn" above.

#### **GLOSSARY OF TERMS – SUBSCRIPTS**

- n = Word number = 0, 1, 2 and 3

- = Bit number = 0 or 1 i

- = Input/Output number(s) associated with cell(s) upon i. which a "Write-in", "Read-out" or other function is being performed.

- Input/Output number(s) other than "i" above. k = =

- м Designation of Memory Cell (word) = eight identical cells in each package.

- в. Examples

- 1.  $I_j$  for bit "1" equals  $I_1$ .

- 2.  $\dot{M}_{nj} = M_{10} = \text{word "1" bit "0".}$

- 3.  $Y_i = 0$ ,  $Y_k = 1$ : for i = words 1 and 3; then k = words 0 and 2;  $Y_k = 0$  and 5 and 2:  $Y_{1,3} = 0$  and  $Y_{0,2} = 1$ .

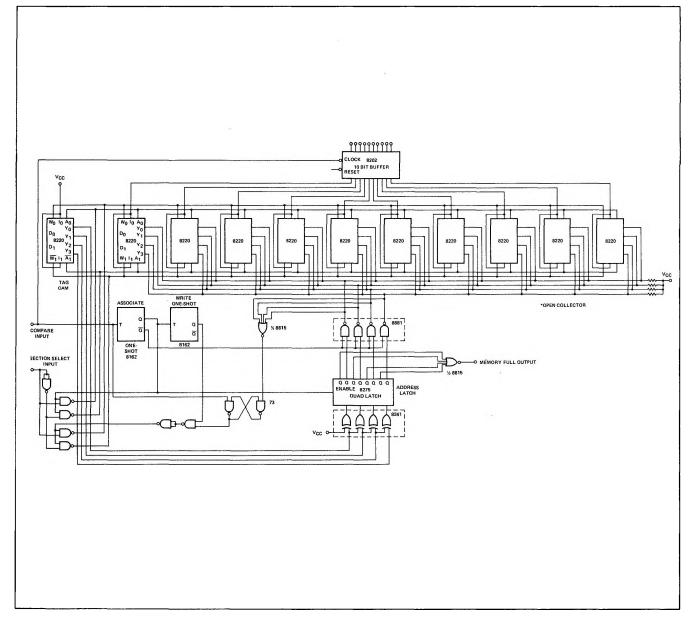

## APPLICATION: LEARNING MEMORY

This system is a CAM array with peripheral IC circuitry designed to operate as a learning memory. It is organized in two sections of equal capacity, the total memory size (both sections) being 8 ten bit words. Either section can be selected through the section SELECT line, and the memory is easily expandable in the number of words and in word length.

By activating the COMPARE line, a new word is loaded into the buffer and is presented to the memory. Through the novel feature of data association, which is unique with CAM elements, the buffer's content is compared with the words stored in memory. If the input word, with which the memory was presented, is already contained in storage, no need for "learning" i.e. data acquisition, exists. This fact is indicated by a match from one of the  $Y_n$  lines ( $Y_i = 1$ ) and thus

## **APPLICATION: LEARNING MEMORY**

no write command is initiated.

Before a WRITE operation is initiated, a location select has to be made such that the word to be written into the memory will go to the proper place. For this reason, a tag CAM is employed to keep track of memory locations, both empty and full. When a word is written into memory, a "1" is simultaneously written into the tag CAM. Thus, it is possible to keep track of the filled memory locations.

By monitoring the  $Y_n$  lines of the tag CAM, a convenient way of decoding an available address exists. Here exclusive OR circuitry is used which ensures that memory locations are filled successively when the need for "learning" exists. The quad latch is enabled before the write command is available to the CAM array. Thus the Y lines of unavailable memory locations are forced low (Y<sub>k</sub> = 0).