# INTEGRATED CIRCUITS

Product specification

1995 January

IC20 Data Handbook

HILIP

Philips Semiconductors

### 80CL31/80CL51

#### **FEATURES**

- Full static 80C51 CPU

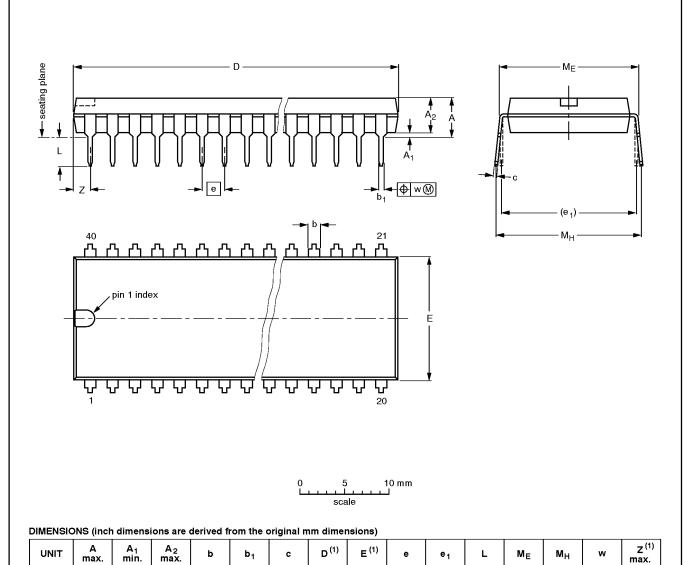

- 8-bit CPU, ROM, RAM, 1/0 in a single 40-lead DIL / mini-pack

- 4K x 8 ROM, expandable externally to 64K bytes

- 128 bytes RAM, expandable externally to 64K bytes

- Four 8-bit ports, 321/0 lines

- Two 16-bit timer / event counters

- External memory expandable up to 128K, external ROM up to 64K and / or RAM up to 64K

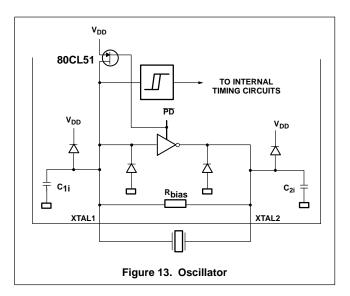

- On-chip oscillator suitable for RC, LC, quartz crystal or ceramic resonator

- Thirteen source, thirteen vector interrupt structure with two priority levels

- Full duplex serial port (UART)

- Enhanced architecture with:

- non-page oriented instructions

- direct addressing

- four eight byte RAM register banks

- stack depth up to 128 bytes

- multiply, divide, subtract and compare instructions

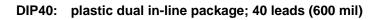

- Power-Down and IDLE instructions

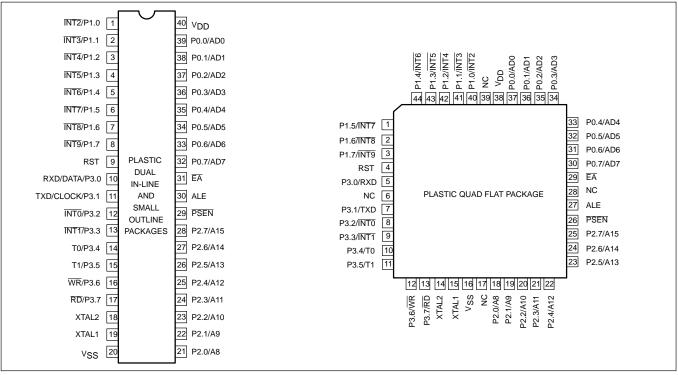

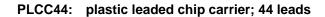

### **PIN CONFIGURATIONS**

- Wake-up via external interrupts at Port 1

- Single supply voltage of 1.8V to 6.0V (5.0V ±10% for P80C51)

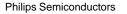

- Frequency range of 0 to 16MHz (3.5MHz to 16MHz for P80C51)

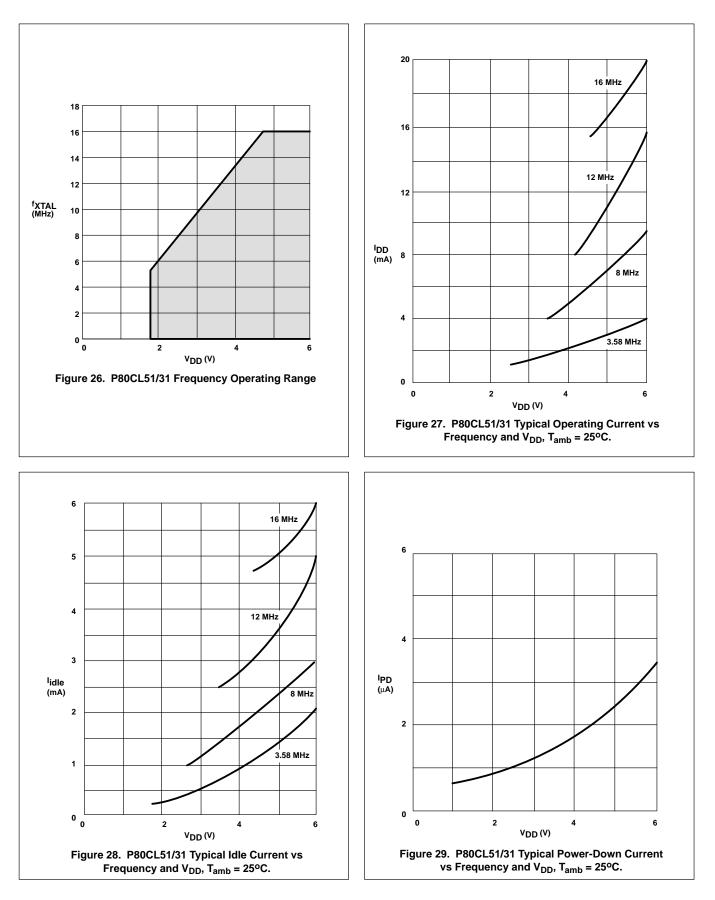

- Very low current consumption

- Operating temperature range: -40 to +85°C

#### DESCRIPTION

The 80CL51 is manufactured in an advanced CMOS technology. The instruction set of the 80CL51 is based on that of the 8051. The 80CL51 is a general purpose microcontroller especially suited for battery-powered applications. The device has low power consumption and a wide range of supply voltage. For emulation purposes, the 85CL000 (Piggy-back version) with 256 bytes of RAM is recommended. The 80CL51 has two software selectable modes of reduced activity for further power reduction: Idle and Power-down. The 80CL51 also functions as an arithmetic processor having facilities for both binary and BCD arithmetic plus bit-handling capabilities. The instruction set consists of over 100 instructions: 49 one-byte, 46 two-byte, and 16 three-byte.

The P80CL31 is the ROMless version of the P80CL51. P80C51 is a 5V version of the low voltage P80CL51.

The P80CL31 is the ROMless version of the P80CL51. P80C51 is a 5V version of the low voltage P80CL51.

### 80CL31/80CL51

### **ORDERING INFORMATION**

| PHILIPS PA<br>NUMBER PA | RT ORDER<br>RT MARKING |              | PHILIPS NORTH AMERICA <sup>1</sup><br>PART ORDER NUMBER TEMPERATURE RANGE |                                                                        |          |

|-------------------------|------------------------|--------------|---------------------------------------------------------------------------|------------------------------------------------------------------------|----------|

| ROMIess                 | ROM                    | ROMIess      | ROM                                                                       | AND PACKAGE                                                            | NUMBER   |

| P80CL31HFP              | P80CL51HFP             | P80CL31HFP N | P80CL51HFP N                                                              | –40 to +85;<br>40-lead Plastic Dual In-line Package (1.8V to 6V)       | SOT129-1 |

| P80CL31HFT              | P80CL51HFT             | P80CL31HFT D | P80CL51HFT D                                                              | -40 to +85;<br>40-lead Plastic Small Outline Package (1.8V to 6V)      | SOT158-1 |

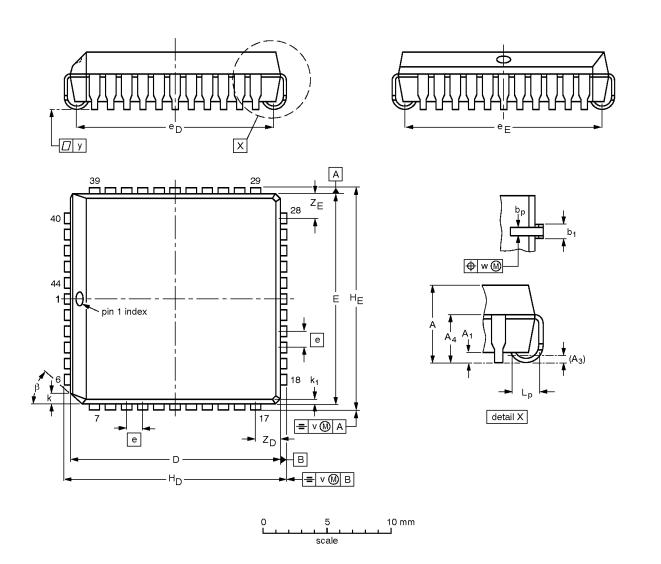

| P80CL31HFH              | P80CL51HFH             | P80CL31HFH B | P80CL51HFH B                                                              | –40 to +85;<br>44-lead Plastic Quad Flat Package (1.8V to 6V)          | SOT307-2 |

|                         | P80C51HFP              |              | P80C51HFP N                                                               | –40 to +85;<br>40-lead Plastic Dual In-line Package (5.0V ±10%)        | SOT129-1 |

|                         | P80C51HFT              |              | P80C51HFT D                                                               | $-40$ to +85; 40-lead Plastic Small Outline Package (5.0V $\pm 10\%$ ) | SOT158-1 |

|                         | P80C51HFH              |              | P80C51HFH B                                                               | -40 to +85;<br>44-lead Plastic Quad Flat Package (5.0V $\pm 10\%$ )    | SOT307-2 |

#### NOTE:

1. Parts ordered by the Philips North America part number will be marked with the Philips part marking.

# 80CL31/80CL51

### **PIN DESCRIPTIONS**

| PIN      |          |                        |                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|----------|----------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| QFP      | DIP      | DESIGNATION            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| 40       | 1        | P1.O/INT2              | Port 1: Port 1 is an 8-bit bidirectional I/O port with internal pullups. Port 1 pins that have 1s written                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 41       | 2        | P1.1/INT3              | to them are pulled HIGH by the internal pullups, and in that state can be used as inputs. The Port 1                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

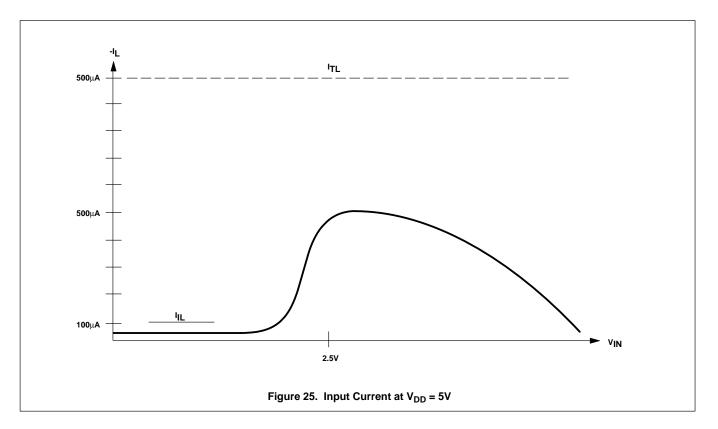

| 42       | 3        | P1.2/INT4              | output buffer can sink/source 4 LS TTL loads. As inputs, Port 1 pins that are externally pulled LOW will source current ( $I_{IL}$ in the characteristics) due to the internal pullups. Port 1 also serves the                                                                                                                                                                                                       |  |  |  |  |  |  |

| 43       | 4        | P1.3/INT5              | alternative functions INT2 to INT9.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| 44       | 5        | P1.4/INT6              |                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| 1        | 6        | P1.5/INT7              |                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| 23       | 7<br>8   | P1.6/INT8<br>P1.7/INT9 |                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|          |          |                        |                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| 4        | 9        | RST                    | Reset: A high level on this pin for two machine cycles while the oscillator is running resets the device.                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 5–13     | 10-17    |                        | <b>Port 3:</b> Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. The Port 3 output buffers can sink/source 4 LS TTL inputs. Port 3 pins that have 1s written to them are pulled HIGH by the internal pull ups, and in that state can be used as inputs. As inputs, Port 3 pins that are externally pulled LOW will source current ( $I_{IL}$ in the characteristics) due to the internal pull ups.   |  |  |  |  |  |  |

| 5        | 10       | P3.0/RXD/data          | RXD/data: Serial port receiver data input (asynchronous)or data input/output (synchronous)                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| 7        | 11       | P3.1/TXD/clock         | TXD/clock: Serial port transmitter data output (asynchronous) or clock output (synchronous)                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 8        | 12       | P3.2/INT0              | INTO: External interrupt 0.                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 9        | 13       | P3.3/INT1              | INT1: External interrupt 1.                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 10       | 14       | P3.4/T0                | T0: Timer 0 external input.                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 11<br>12 | 15<br>16 | P3.5/T1<br>P3.6/WR     | T1: Timer 1 external input.<br>WR: External data memory write strobe.                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| 12       | 10       | P3.7/RD                | <b>RD</b> : External data memory read strobe.                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| 14       | 18       | XTAL2                  | Crystal output: Output of the inverting amplifier of the oscillator. Left open when external clock is used.                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|          |          |                        | Crystal input: Input to the inverting amplifier of the oscillator; also the input for an externally gen-<br>erated clock source.                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| 15       | 19       | XTAL1                  | <b>Crystal input:</b> Input to the inverting amplifier of the oscillator; also the input for an externally generated clock source.                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| 16       | 20       | Vss                    | Ground: Circuit ground potential.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| 18-25    | 21-28    | P2.0-P2.7              | <b>Port 2:</b> Port 2 is an 8-bit bidirectional 1/0 port with internal pullups. Port 2 pins that have 1s written to them are pulled HIGH by the internal pullups, and in that state can be used as inputs. The Port 2 output buffer can sink/source 4 LS TTL loads.                                                                                                                                                  |  |  |  |  |  |  |

|          |          |                        | Port 2 emits the high-order address byte during accesses to external memory that use 1 6-bit ad-<br>dresses (MOVX @DPTR). In this application it uses the strong internal pullups when emitting 1s.<br>During accesses to external memory that use 8-bit addresses (MOVX @Ri), Port 2 emits the con-<br>tents of the P2 Special Function Register.                                                                   |  |  |  |  |  |  |

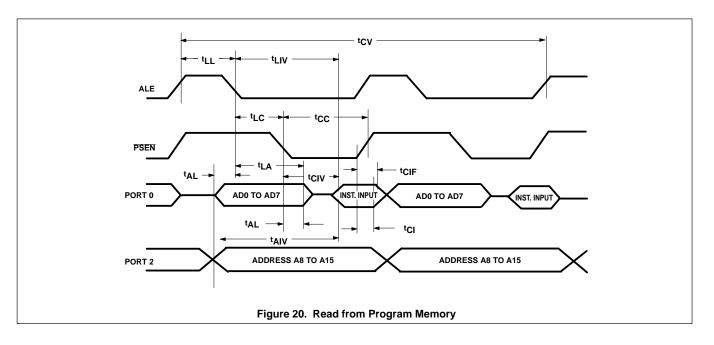

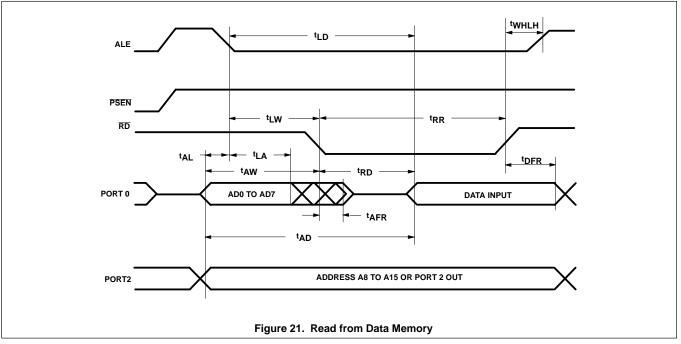

| 26       | 29       | PSEN                   | <b>Program store enable output:</b> Read strobe to external program memory. When executing code out of external program memory, PSEN is activated twice each machine cycle. However, during each access to external data memory two PSEN activations are skipped.                                                                                                                                                    |  |  |  |  |  |  |

| 27       | 30       | ALE                    | Address Latch Enable: Output pulse for latching the low byte of the address during access to external memory. ALE is emitted at a constant rate of 1/6 of the oscillator frequency, and may be used for external timing or clocking purposes.                                                                                                                                                                        |  |  |  |  |  |  |

| 29       | 31       | ĒĀ                     | <b>External Access:</b> When EA is held High the CPU executes out of internal program memory (unless the program counter exceeds 0FFFH). Holding EA LOW forces the CPU to execute out of external memory regardless of the value of the program counter.                                                                                                                                                             |  |  |  |  |  |  |

| 30-37    | 32-39    | P0.0-P00.7             | <b>Port 0:</b> Port 0 is an 8-bit open drain bidirectional I/O port. As an open drain output port it can sink 8 LS TTL loads. Port 0 pins that have 1s written to them float, and in that state will function as high impedance inputs. Port 0 is also the multiplexed low order address and data bus during access to external memory. In this application it uses strong internal pull-ups when emitting logic 1s. |  |  |  |  |  |  |

| 38       | 40       | V <sub>DD</sub>        | Power supply.                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

### 80CL31/80CL51

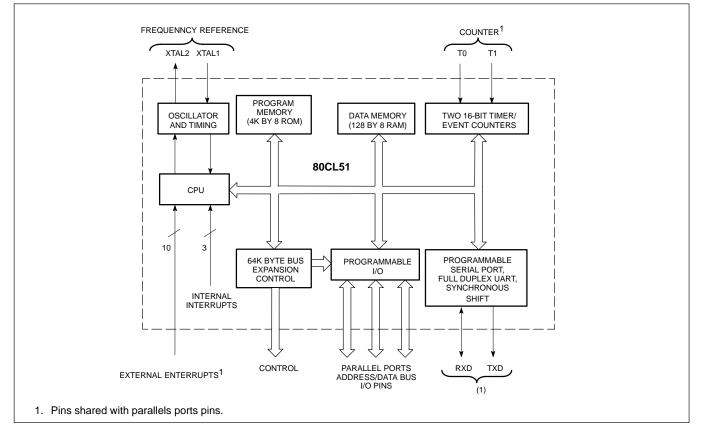

### **BLOCK DIAGRAM**

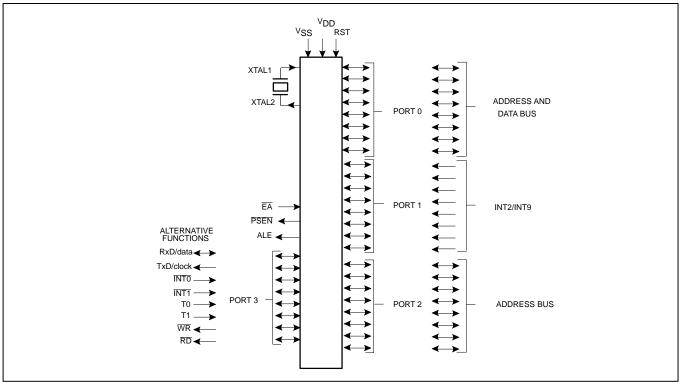

### FUNCTIONAL DIAGRAM

### 80CL31/80CL51

#### **1.0 FUNCTIONAL DESCRIPTION**

#### General

The 80CL51 is a stand-alone high-performance CMOS microcontroller designed for use in real-time applications such as instrumentation, industrial control, intelligent computer peripherals and consumer products.

The device provides hardware features, architectural enhancements and new instructions to function as a controller for applications requiring up to 64K bytes of program memory and/or up to 64K bytes of data storage.

The 80CL51 contains a non-volatile 4K byte  $\times$  8 read-only program memory; a static 128 byte  $\times$  8 read/write data memory; 32 1/0 lines; two 16-bit timer/event counters; a thirteen- source two priority-level, nested interrupt structure and on-chip oscillator and timing circuit.

The device has two software selectable modes of reduced activity for power reduction: IDLE and Power-down. The Idle mode freezes the CPU while allowing the RAM, timers, serial I/O and interrupt system to continue functioning. The Power-down mode saves the RAM contents but freezes the oscillator causing all other chip functions to be inoperative.

The P80C51 is a 5V version of the low voltage microcontroller P80CL51. Hereafter the generic term P80CL51 will be used for the functional description of both types. The special features of the P80C51 are handled in chapter 1.9.

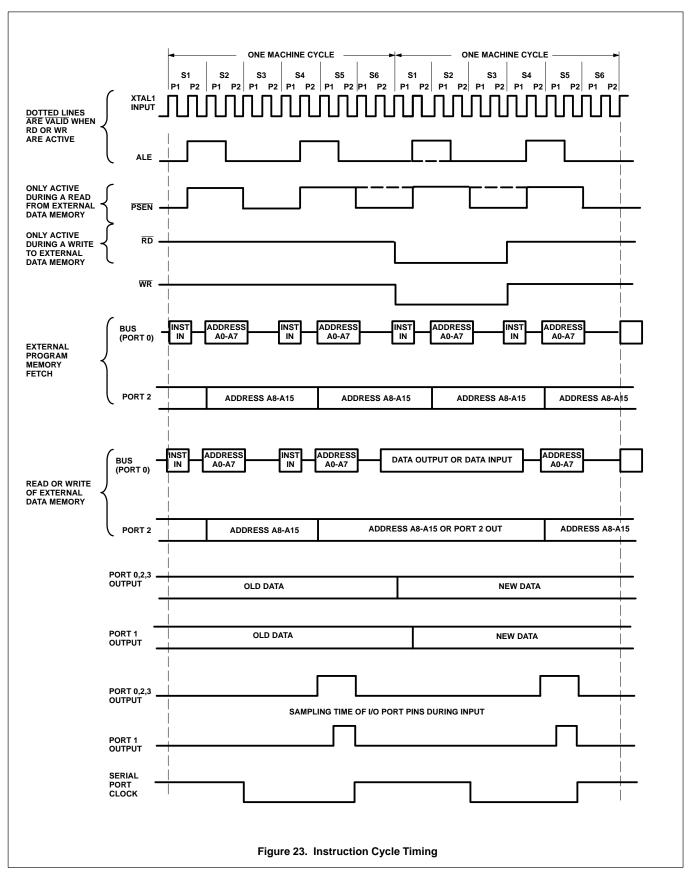

#### CPU timing

A machine cycle consists of a sequence of 6 states. Each state time lasts for two oscillator periods, thus a machine cycle takes 12 oscillator periods or  $1\mu$ s if the oscillator frequency is 12MHz.

#### 1.1 Memory organization

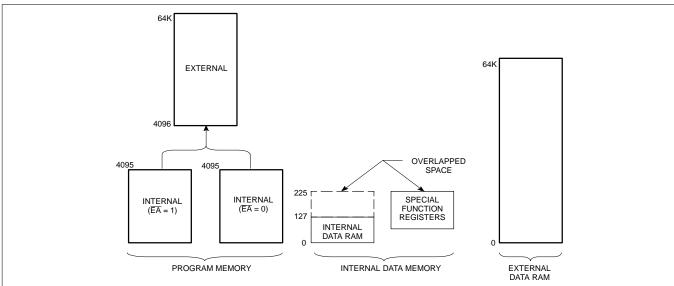

The 80CL51 has a 4K Program Memory (ROM) plus 128 bytes of Data Memory (RAM) on board. The device has separate address spaces for Program and Data Memory (see Memory Map). Using Ports P0 and P2, the 80CL51 can address up to 64K bytes of external memory. The CPU generates both read and write signals (RD and WR) for external Data Memory accesses, and the read strobe (PSEN) for external Program Memory.

#### 1.1.1 Program Memory

The 80CL51 contains 4K bytes of internal ROM. After reset the CPU begins execution at location 0000H. The lower 4K bytes of Program Memory can be implemented in either on- chip ROM or external Memory. If the EA pin is strapped to  $V_{DD}$ , then program memory fetches from addresses 000H through 0FFFH are directed to the internal ROM. Fetches from addresses 1000H through FFFFH are directed to external ROM. Program counter values greater than 0FFFH are automatically addressed to external memory regardless of the state of the EA pin.

#### 1.1.2 Data Memory

The 80CL51 contains 128 bytes of internal RAM and 25 Special Function Registers (SFR). The Memory Map below shows the internal Data Memory space divided into the Lower 128, the Upper 128, and the SFR space.

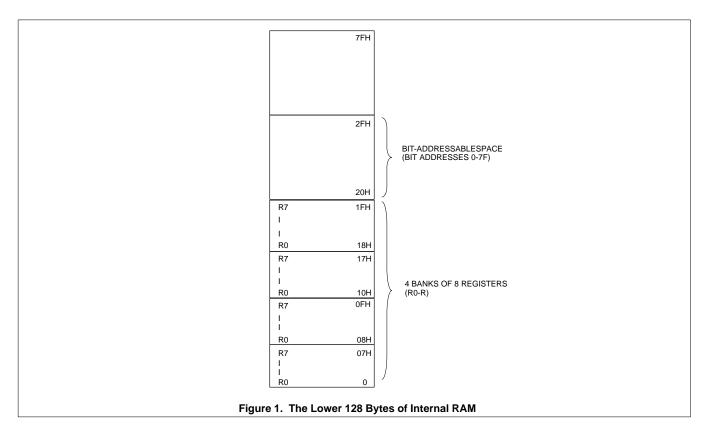

The lower 128 bytes of the internal RAM are organized as mapped in Figure 1. The lowest 32 bytes are grouped into 4 banks of 8 registers. Program instructions refer to these registers R0 through R7. Two bits in the Program Status Word select which register bank is in use. The next 16 bytes above the register banks form a block of bit-addressable memory space. The 128 bits in this area can be directly addressed by the single-bit manipulation instructions. The remaining registers (30H to 7FH) are directly and indirectly byte addressable.

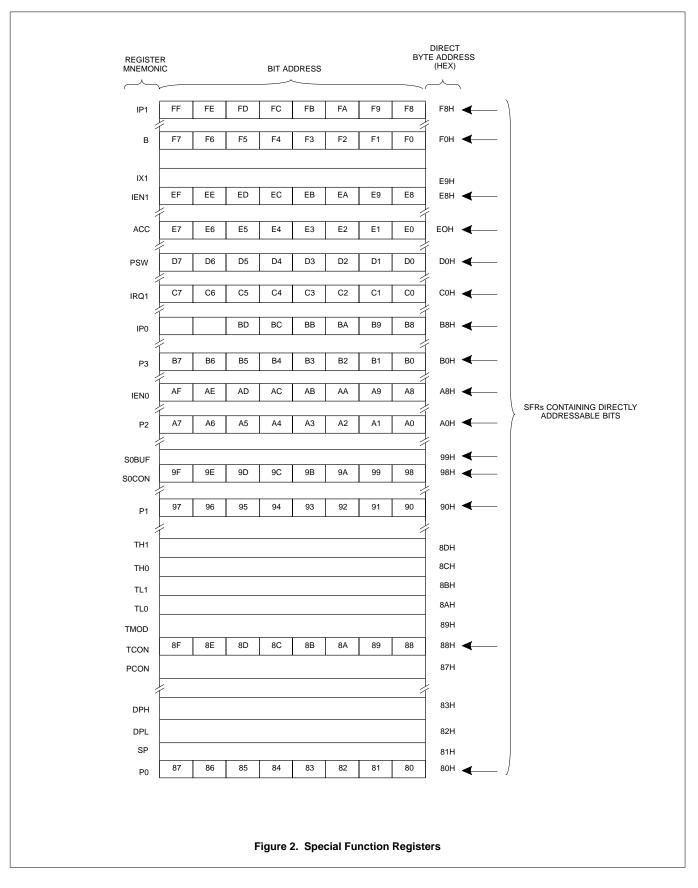

#### 1.1.3 Special Function Registers

The upper 128 bytes are the address locations of the SFRs. Figure 2 shows the Special Function Register (SFR) space. SFRs include the port latches, timers, peripheral control, serial I/O registers, etc. These registers can only be accessed by direct addressing. There are 128 addressable locations in the SFR address space (SFRs with addresses divisible by eight).

#### 1.1.4 Addressing

The 80CL51 has five methods for addressing source operands:

- Register

- Direct

- Register-Indirect

- Immediate

- Base-Register-plus Index-Register-indirect

#### MEMORY MAP

#### Product specification

### Low-voltage single-chip 8-bit microcontrollers

### 80CL31/80CL51

The first three methods can be used for addressing destination operands. Most instructions have a "destination/source" filed that specifies data type, addressing methods and operands involved. For operations other than MOVs, the destination operand is also a source operand.

Access to memory addressing is as follows:

- Registers in one of the four register banks through register, direct or indirect.

- Internal RAM (128 bytes) through direct or register-indirect.

- Special Function Register through Direct.

- External data memory through Register-Indirect

- Program memory look-up tables through Base-Register-Plus Index-Register-Indirect.

#### 1.2 I/O Facilities

#### 1.2.1 Ports

The 80CL51 has 32 I/O lines treated as 32 individually addressable bits or as four parallel 8- bit addressable ports. Port 0, 1, 2 and 3 perform the following alternate functions:

- Port 0: provides the multiplexed low-order address and data bus for expanding the device with standard memories and peripherals.

- Port 1: provides the inputs for the external interrupts INT2/INT9.

- Port 2: provides the high-order address when expanding the device with external program or data memory.

- Port 3: pins can be configured individually to provide: (1) external interrupt request inputs

- (2) counter input

- (3) control signals to read and write to external memories (4) UART input and output

To enable a Port 3 pin alternate function, the Port 3 bit latch in its SFR must contain a logic 1.

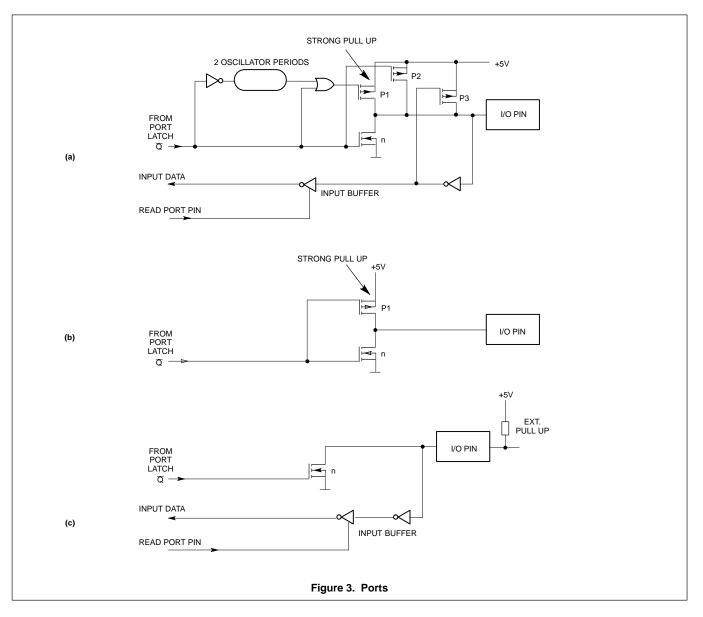

Each port consists of a latch (Special Function Registers P0 to P3), an output driver and an input buffer. Ports 1,2,3 have internal pull ups. Figure 3(a) shows that the strong transistor p1 is turned on for only 2 oscillator periods after a 0-to-1 transition in the port latch. When on, it turns on p3 (a weak pull up) through the inverter. This inverter and p3 form a latch which hold the 1. In Port 0 the pull up p1 is only on when emitting 1s for external memory access. Writing a 1 to a Port 0 bit latch leaves both output transistors switched off so the pin can be used as a high-impedance input.

#### 1.2.2 Port Options

The pins of port 1, port 2, and port 3 may be individually configured with one of the following options (see Figure 3):

- Option 1: Standard Port; quasi-bidirectional I/O with pull up. The strong booster pull up p1 is turned on for two oscillator periods after a 0-to-1 transition in the port latch (see Figure 3(a)).

- Option 2: Open drain; guasi-bidirectional I/O with n-channel open drain output. Use as an output requires the connection of an external pull up resistor (see Figure 3(c)).

- Option 3: Push-Pull; output with drive capability in both polarities. Under this option, pins can only be used as outputs. See Figure 3(b).

### 80CL31/80CL51

The definition of port options for port 0 is slightly different. Two cases have to be examined. First, accesses to external memory (EA=0 or access above the built -in memory boundary), second, I/O accesses.

#### External Memory Accesses

- Option 1: True 0 and 1 are written as address to the external memory (strong pull up is used).

- Option 2: An external pull up resistor is needed for external accesses.

- Option 3: Not allowed for external memory access as the port can only be used as output.

#### I/O Accesses

Option 1: When writing a 1 to the port-latch, the strong pull up p1 will be on for 2 oscillator periods. No weak pull up exists. Without an external pull up, this option can be used as a high-impedance input.

- Option 2: Open drain; quasi-bidirectional I/O with n-channel open drain output. Use as an output requires the connection of an external pull up resistor (see Figure 3(c)).

- Option 3: Push-Pull; output with drive capability in both polarities. Under this option, pins can only be used as outputs.

Individual mask selection of the post-reset state is available on any of the above pins. Make your selection by appending "S" or "R" to option 1, 2, or 3 above (e.g. 1 S for a standard I/O to be set after RESET or 2R for an open-drain I/O to be reset after RESET).

#### 1.3 Timer/event counter

The 80CL51 contains two 16-bit Timer/Counter registers, Timer 0 and Timer 1, which can perform the following functions:

- Measure time intervals and pulse durations

- Count events

- Generate interrupts requests

#### Product specification

### Low-voltage single-chip 8-bit microcontrollers

### 80CL31/80CL51

Timer 0 and Timer 1 can be independently programmed to operate as follows:

- Mode 0 8-bit timer or counter with divide-by-32 prescaler

- Mode 1 16-bit time-interval or event counter

- Mode 2 8-bit time interval or event counter with automatic reload upon overflow

- Mode 3 Timer 0 establishes TL0 and TH0 as two separate counters.

In the "Timer" function, the register is incremented every machine cycle. Since a machine cycle consists of 12 oscillator periods, the count rate is 1/12 of the oscillator frequency.

In the "Counter" function, the register is incremented in response to a 1-to-0 transition. Since it takes 2 machine cycles (24 oscillator periods) to recognize a 1-to-0 transition, the maximum count rate is 1/24 of the oscillator frequency. To ensure a given level is sampled, it should be held for at least one full machine cycle.

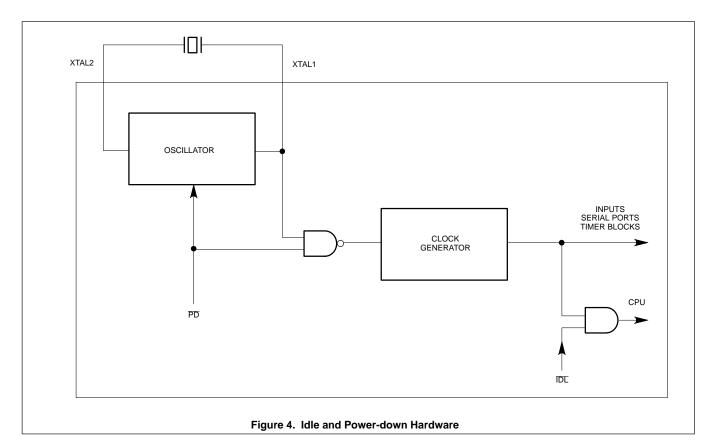

#### 1.4 Idle and Power-down operation

Idle mode operation permits the interrupt, serial port and timer blocks to continue functioning while the clock to the CPU is halted. The following functions remain active during Idle mode:

- Timer 0, Timer 1

- UART

- External interrupt

The Power-down operation freezes the oscillator. The Power-down mode can only be activated by setting the PD bit in the PCON register.

#### 1.4.1 Power control register

Power-down and Idle modes are activated by software via the Special Function Register PCON. Its hardware address is 87H. PCON is byte addressable only.

|      | PCON                    |                                                                            |  |  |  |  |  |  |  |

|------|-------------------------|----------------------------------------------------------------------------|--|--|--|--|--|--|--|

| BIT  | POSITION                | FUNCTION                                                                   |  |  |  |  |  |  |  |

| SMOD | PCON.7<br>PCON.4-PCON.6 | Double baud-rate bit, see description of the UART, chapter 1.5. (reserved) |  |  |  |  |  |  |  |

| GF1  | PCON.3                  | General purpose flag bit                                                   |  |  |  |  |  |  |  |

| GFO  | PCON.2                  | General purpose flag bit                                                   |  |  |  |  |  |  |  |

| PD   | PCON.1                  | Power-down activation bit                                                  |  |  |  |  |  |  |  |

| IDL  | PCON.0                  | Idle mode activation bit                                                   |  |  |  |  |  |  |  |

#### 10

### 80CL31/80CL51

#### 1.4.2 Power-down mode

The instruction setting PCON.1 is the last executed prior to going into the Power-down mode. In Power-down mode the oscillator is stopped. The contents of the on-chip RAM and SFRs are preserved. The port pins output the values held by their respective SFRs. ALE and PSEN are held LOW.

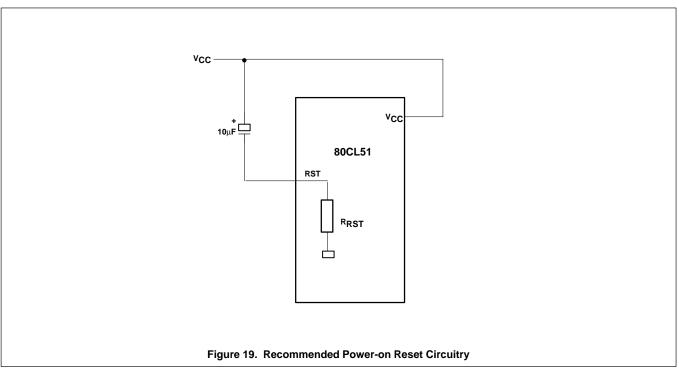

In the Power-down mode  $V_{DD}$  may be reduced to minimize power consumption. However, the supply voltage must not be reduced until Power-down mode is active, and must be restored before the hardware reset is applied and frees the oscillator. Reset must be held active until the oscillator has restarted and stabilized.

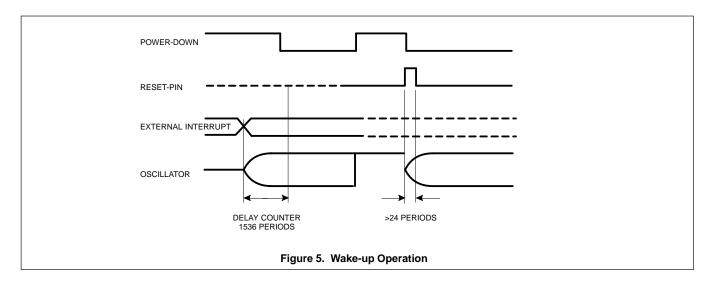

The wake-up operation after power-down in this controller has two basic approaches:

#### 1.4.2.1 Wake-up using INT2 to INT9

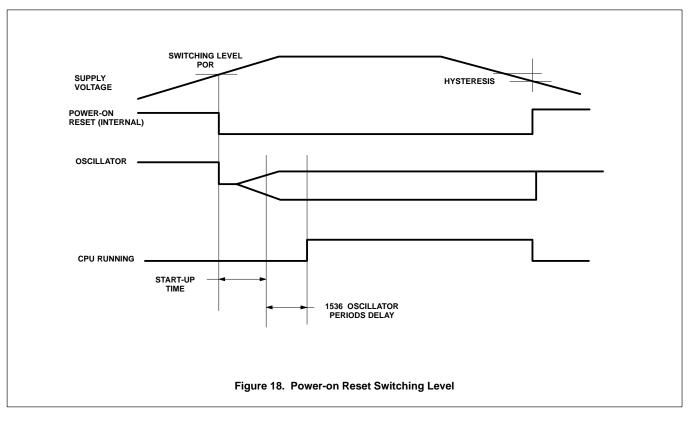

If INT2 to INT9 are enabled, the 80CL51 can be awakened from power-down mode with the external interrupts. To ensure that the oscillator is stable before the controller restarts, the internal clock will remain inactive for 1536 oscillator periods. This is controlled by an on-chip delay counter.

#### 1.4.2.2 Wake-up using RESET

To wake-up the 80CL51 the RESET pin has to be kept HIGH for a minimum of 24 oscillator periods. The on-chip delay counter is inactive. The user has to ensure that the oscillator is stable before any operation is attempted. Figure 5 illustrates the two possibilities for wake-up.

#### 1.4.3 Idle mode

The instruction that sets PCON.0 is the last instruction executed before going into Idle mode. Once in the Idle mode, the internal

clock is gated away from the CPU, but not from the Interrupt, Timer and Serial port functions. The CPU status is preserved along with the Stack Pointer, Program Counter, Program Status Word and Accumulator. The RAM and all other registers maintain their data during Idle mode. The port pins retain the logical states they held at Idle mode activation. ALE and PSEN hold at the logic HIGH level.

There are two methods used to terminate the Idle mode. Activation of any enabled interrupt will cause PCON to be cleared by hardware, terminating Idle mode. The interrupt is serviced, and following the instruction RETI, the next instruction to be executed will be the one following the instruction that put the device in the Idle mode.

Flag bits GF0 and GF1 may be used to determine whether the interrupt was received during normal execution or Idle mode. For example, the instruction that writes to PCON.0 can also set or clear one or both flag bits. When Idle mode is terminated by an interrupt, the service routine can examine the status of the flag bits.

The second method of terminating the Idle mode is with an external hardware reset. Since the oscillator is still running, the hardware reset is required to be active for only two machine cycles to complete the reset operation.

Reset redefines all SFRs, but does not affect the on-chip RAM.

The status of the external pins during Idle and Power-down mode is shown in Table 1. If the Power-down mode is activated while accessing external memory, port data held in the Special Function Register P2 is restored to Port 2. If the data is a logic 1, the port pin is held HIGH during the Power-down mode by the strong pull up transistor p1 (see Figure 3(a)).

| MODE       | MEMORY   | ALE | PSEN | PORT 0    | PORT 1    | PORT 2    | PORT 3    |

|------------|----------|-----|------|-----------|-----------|-----------|-----------|

| Idle       | internal | 1   | 1    | Port Data | Port Data | Port Data | Port Data |

| Idle       | external | 1   | 1    | Floating  | Port Data | Address   | Port Data |

| Power-down | internal | 0   | 0    | Port Data | Port Data | Port Data | Port Data |

| Power-down | external | 0   | 0    | Floating  | Port Data | Port Data | Port Data |

# 80CL31/80CL51

### 1.5 Standard serial interface SI0: UART

This serial port is full duplex, meaning it can transmit and receive simultaneously. It is also receive-buffered, meaning it can commence reception of a second byte before a previously received byte has been read from the register. (However, if the first byte still hasn't been read by the time reception of the second byte is complete, one of the bytes will be lost). The serial port receive and transmit registers are both accessed at Special Function Register SOBUF. Writing to SOBUF loads the transmit register, and reading SOBUF loads the transmit register, and reading SOBUF accesses a physically separate receive register.

The serial port can operate in 4 modes:

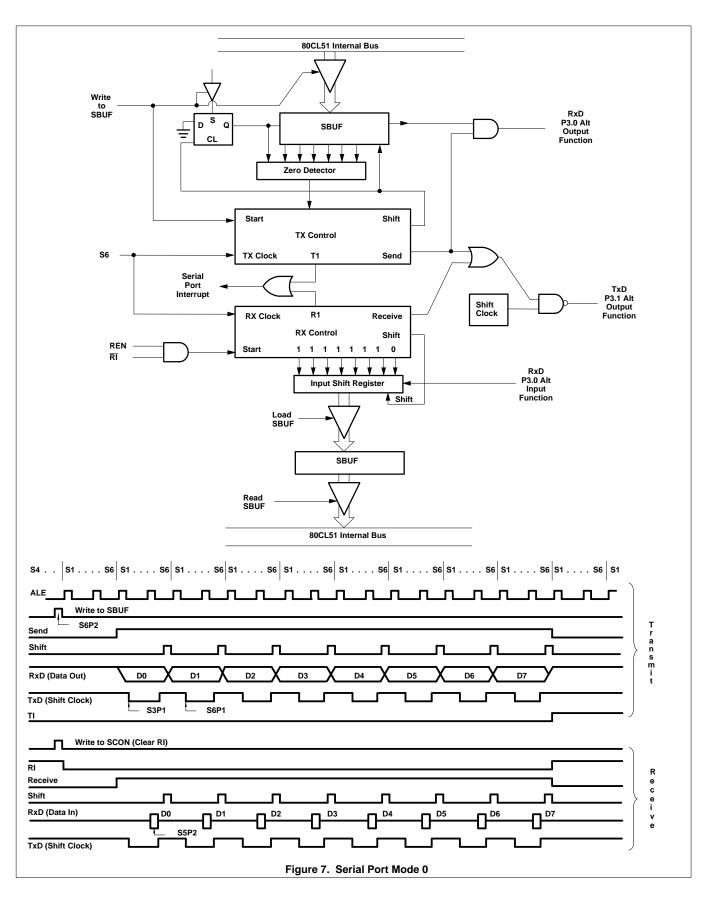

- Mode 0: Serial data enters and exits through RxD. TxD outputs the shift clock. 8 bits are transmitted/ received (LSB first). The baud is fixed at 1/12 the oscillator frequency.

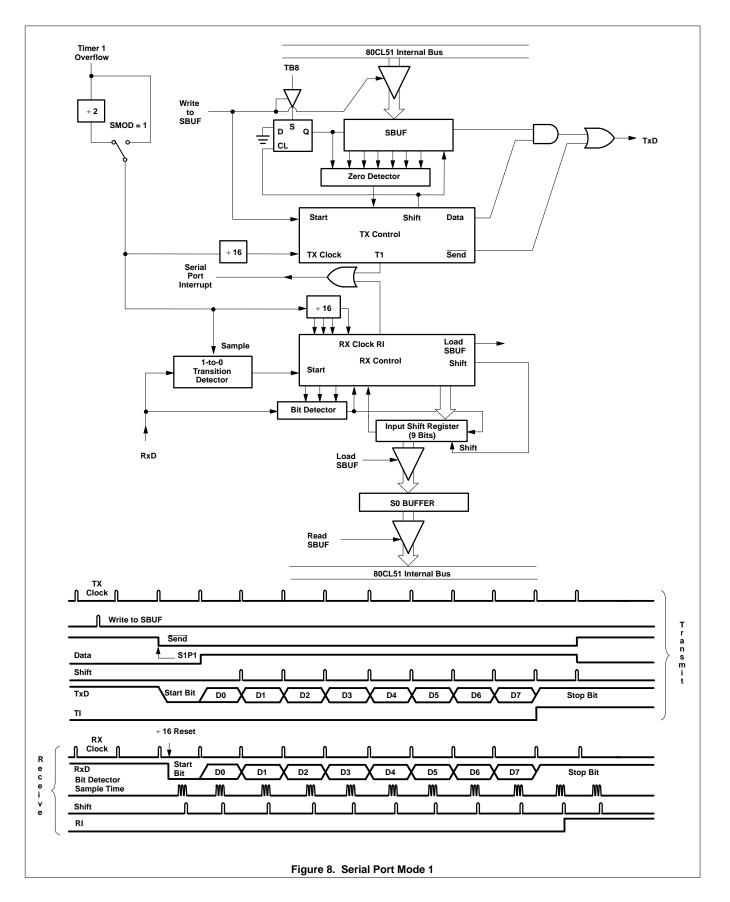

- Mode 1: 10 bits are transmitted (through TxD) or received (through RxD): a start bit (0), 8 data bits (LSB first), and a stop bit (1). On receive, the stop bit goes into RB8 in Special Function Register SCON. The baud rate is variable.

- Mode 2: 11 bits are transmitted (through TxD) or received (through RxD): start bit (0), 8 data bits (LSB first), a programmable 9th data bit, and a stop bit (1). On Transmit, the 9th data bit (TB8 in SCON) can be assigned the value of 0 or 1. Or, for example, the parity bit (P, in the PSW) could be moved into TB8. On receive, the 9th data bit goes into RB8 in Special Function Register SCON, while the stop bit is ignored. The baud rate is programmable to either 1/32 or 1/64 the oscillator frequency.

- Mode 3: 11 bits are transmitted (through TxD) or received (through RxD): a start bit (0), 8 data bits (LSB first), a programmable 9th data bit and a stop bit (1). In fact, Mode 3 is the same as Mode 2 in all respects except baud rate. The baud rate in Mode 3 is variable.

In all four modes, transmission is initiated by any instruction that uses S0BUF as a destination register. Reception is initiated in Mode 0 by the condition RI = 0 and REN = 1. Reception is initiated in the other modes by the incoming start bit if REN = 1.

### 1.5.1 Multiprocessor communications

Modes 2 and 3 have a special provision for multiprocessor communications. In these modes, 9 data bits are received. The 9th one goes into RB8. Then comes a stop bit. The port can be programmed such that when the stop bit is received, the serial port interrupt will be activated only if RB8 = 1. This feature is enabled by setting bit SM2 in SCON. A way to use this feature in multiprocessor systems is as follows:

When the master processor wants to transmit a block of data to one of several slaves, it first sends out an address byte which identifies the target slave. An address byte differs from a data byte in that the 9th bit is 1 in an address byte and 0 in a data byte. With SM2 = 1, no slave will be interrupted by a data byte. An address byte, however, will interrupt all slaves, so that each slave can examine the received byte and see if it is being addressed. The addressed slave will clear its SM2 bit and prepare to receive the data bytes that will be coming. The slaves that weren't being addressed leave their SM2s set and go on about their business, ignoring the coming data bytes.

SM2 has no effect in Mode 0, and in Mode 1 can be used to check the validity of the stop bit. In a Mode 1 reception, if SM2 = 1, the receive interrupt will not be activated unless a valid stop bit is received.

### 1.5.2 Serial port control register

The serial port control and status register is the Special Function Register SOCON, shown in Figure 6. The register contains not only the mode selection bits, but also the 9th data bit for transmit and receive (TB8 and RB8), and the serial port interrupt bits (T1 and R1). See next page.

### **Baud Rates**

The baud rate in Mode 0 is fixed: Mode 0 Baud Rate = Oscillator Frequency /12. The baud rate in Mode 2 depends on the value of bit SMOD in Special Function Register PCON. If SMOD = 0 (which is the value on reset), the baud rate is 1/64 the oscillator frequency. If SMOD = 1, the baud rate is 1/32 the oscillator frequency.

Mode 2 Baud Rate = (2<sup>SMOD</sup>/64)(Oscillator Frequency)

The baud rates in Modes 1 and 3 are determined by the Timer 1 overflow rate.

### Using Timer 1 to generate baud rates

When Timer 1 is used as the baud rate generator, the baud rates in Modes 1 and 3 are determined by the Timer 1 overflow rate and the value of SMOD as follows:

(2<sup>SMOD</sup>/32)(Timer 1 Overflow Rate)

The Timer 1 interrupt should be disabled in this application. The Timer itself can be configured for either "timer" or "counter" operation, and in any of its 3 running modes. In the most typical applications, it is configured for "timer operation, in the auto-reload mode (high nibble of TMOD = 0010B). In that case the baud rate is given by the formula:

#### Mode 1, 3 Baud Rate =

$\{(2^{SMOD}/32) \text{ (Oscillator Frequency)} / \{12 (256 - (TH 1 ))\}$

One can achieve very low baud rates with Timer 1 by leaving the Timer 1 interrupt enabled, and configuring this Timer to run as a 16-bit timer (high nibble of TMOD = 0001B), and using the Timer 1 interrupt to do a 16-bit software reload. Table 2 lists various commonly used baud rates and how they can be obtained from Timer 1.

### More about Mode 0

Figure 7 shows a simplified functional diagram of the serial port in Mode 0, and associated timing. Transmission is initiated by any instruction that uses S0BUF as a destination register. The "write to S0BUF" signal at S6P2 also loads a 1 into the 9th position of the transmit shift register and tells the TX Control block to commence a transmission. The internal timing is such that the one full machine cycle will elapse between "write to S0BUF", and activation of SEND.

SEND enables the output of the shift register to the alternate output function line of P3.0 and also enables SHIFT CLOCK to the alternate output function line of P3.1. SHIFT CLOCK is low during S3, S4, and S5 of every machine cycle, and high during S6, S1 and S2. At S6P2 of every machine cycle in which SEND is active, the contents of the transmit shift are shifted to the right one position.

As data bits shift out to the right, zeros come in from the left. When the MSB of the data byte is at the output position of the shift register, then the 1 that was initially loaded into the 9th position is just to the left of the MSB, and all positions to the left of that contain zeros. This condition flags the TX Control block to do one last shift and then deactivate SEND and set T1. Both of these actions occur at S1P1 of the 10th machine cycle after "write to S0BUF".

Reception is initiated by the condition REN = 1 and R1 = 0. At S6P2 of the next machine cycle, the RX Control unit writes the bits 11111110 to the receive shift register, and in the next clock phase activates RECEIVE.

### 80CL31/80CL51

|     |                                                                              |         | MSB      |            |            |         |         |         | LSB                   |                           |                    |

|-----|------------------------------------------------------------------------------|---------|----------|------------|------------|---------|---------|---------|-----------------------|---------------------------|--------------------|

|     |                                                                              |         | SM0      | SM1 SN     | 12 REN     | TB8     | RB8     | T1      | R1                    |                           |                    |

|     |                                                                              | Where   | e SM0,   | SM1 spe    | cify the   | e seria | l port  | mod     | , as follov           | s:                        |                    |

|     |                                                                              | SM0     | SM1      | Mode       | Dese       | criptio | on      |         | Baud Rate             | •                         |                    |

|     |                                                                              | 0       | 0        | 0          | shift      | regist  | er      |         | f <sub>OSC</sub> / 12 |                           |                    |

|     |                                                                              | 0       | 1        | 1          | 8-bit      | UAR     | Т       |         | variable              |                           |                    |

|     |                                                                              | 1       | 0        | 2          | 9-bit      | UAR     | Т       |         | f <sub>OSC</sub> /64  |                           |                    |

|     |                                                                              |         |          |            |            |         |         |         | or                    |                           |                    |

|     |                                                                              |         |          | 3          | o L ''     |         | ble U/  | DT      | f <sub>OSC</sub> /32  |                           |                    |

|     |                                                                              | 1       | 1        | 3          | 9-01       | valla   | Die U/  |         |                       |                           |                    |

| SM2 | Enables the multiproce<br>be activated if the rece<br>was not received. In M | ived 9t | h data   | bit (RB8   | ) is 0. Iı |         |         |         |                       |                           |                    |

| REN | Enables serial receptio                                                      | n. Set  | by soft  | ware to e  | enable     | recep   | tion. C | lear    | y softwar             | e to disable reception.   |                    |

| TB8 | Is the 9th data bit that                                                     | will be | transm   | itted in N | lodes 2    | 2 and   | 3. Set  | or cl   | ar by soft            | ware as desired.          |                    |

| RB8 | In Modes 2 and 3, is th<br>Mode 0, RB8 is not use                            |         | lata bit | that was   | receiv     | ed. In  | Mode    | e 1, it | SM2=0, R              | B8 is the stop bit that v | vas received. In   |

| ті  | Is transmit interrupt flag                                                   | •       | -        |            |            |         |         |         |                       | or at the beginning of t  | he stop bit in the |

|     | other modes, in any se                                                       | nai tia |          |            |            |         |         |         | •                     |                           |                    |

| RI  | other modes, in any se<br>Receive interrupt flag.<br>the other modes, in any | Set by  | hardwa   |            |            |         |         |         | n Mode 0              | , ,                       | e stop bit time in |

### Table 2. Timer 1 Generated Commonly Used Baud Rates

|                       |            |      |     | TIME | R 1          |

|-----------------------|------------|------|-----|------|--------------|

| BAUD RATE             | fosc       | SMOD | С/Т | MODE | RELOAD VALUE |

| Mode 0 Max: 1.33 Mb/s | 16 MHz     | х    | x   | х    | x            |

| Mode 2 Max: 500 Kb/s  | 16 MHz     | 1    | x   | х    | x            |

| Modes 1,3: 83.3 Kb/s  | 16 MHz     | 1    | 0   | 2    | FFH          |

| 19.2 Kb/s             | 11.059 MHz | 1    | 0   | 2    | FDH          |

| 9.6 Kb/s              | 11.059 MHz | 0    | 0   | 2    | FDH          |

| 4.8 Kb/s              | 11.059 MHz | 0    | 0   | 2    | FAH          |

| 2.4 Kb/s              | 11.059 MHz | 0    | 0   | 2    | F4H          |

| 1.2 Kb/s              | 11.059 MHz | 0    | 0   | 2    | E8H          |

| 137.5 Kb/s            | 11.986 MHz | 0    | 0   | 2    | 1DH          |

| 110                   | 6 MHz      | 0    | 0   | 2    | 72H          |

| 110                   | 12 MHz     | 0    | 0   | 1    | FEEBH        |

80CL31/80CL51

RECEIVE enables SHIFT CLOCK to the alternate output function line of P3.1. SHIFT Clock makes transitions at S3P1 and S6P1 of every machine cycle. at S6P2 of every machine cycle in which RECEIVE is active, the contents of the receive shift register are shifted to the left one position. The value that comes in from the right is the value that was sampled at the P3.0 pin at S5P2 of the same machine cycle.

As data bits come in from the right, 1s shift out to the left. When the 0 that was initially loaded into the right-most position arrives at the left-most position in the shift register, it flags the RX Control block to do one last shift and load S0BUF. At S1P1 of the 10th machine cycle after the write to SCON that cleared RI, RECEIVE is cleared as RI is set.

#### More about Mode 1

Ten bits are transmitted (through TxD), or received (through RxD): a start bit (0), 8 data bits (LSB first), and a stop bit (1). On receive, the stop bit goes into RB8 in SCON. In the 8051 the baud rate is determined by the Timer 1 overflow rate.

Figure 8 shows a simplified functional diagram of the serial port in Mode 1, and associated timings for transmit/receive.

Transmission is initiated by any instruction that uses S0BUF as a destination register. The "write to S0BUF" signal also loads a 1 into the 9th bit position of the transmit shift register and flags the TX Control unit that a transmission is requested. Transmission actually commences at S1P1 of the machine cycle following the next rollover in the divide-by-16 counter. (Thus, the bit times are synchronized to the divide-by-16 counter, not to the "write to S0BUF" signal).

The transmission begins with activation of SEND which sends the start bit to pin TxD. One bit time later, DATA is activated, enabling the transmission of the output bit of the transmit shift register to TxD. The first shift pulse occurs one bit time after that.

As data bits shift out to the right, zeros are clocked in from the left. When the MSB of the data byte is at the output position of the shift register, then the 1 that was initially loaded into the 9th position is just to the left of the MSB, and all positions to the left of that contain zeros. This condition flags the TX Control unit to do one last shift and then deactivate SEND and set TI. This occurs at the 10th divide-by-16 rollover after "write to S0BUF". Reception is initiated by a detected 1 -to-0 transition at RxD. For this purpose RxD is sampled at a rate of 16 times whatever baud rate has been established. When a transition is detected, the divide-by-16 counter is immediately reset, and 1FFH is written into the input shift register. Resetting the divide-by-16 counter aligns its rollovers with the boundaries of the incoming bit times. The 16 states of the counter divide each bit time into 16th. At the 7th, 8th, and 9th counter states of each bit time, the bit detector samples the value of RxD. The value accepted is the value that was seen in at least 2 of the 3 samples. This is done for noise rejection. If the value accepted during the first bit time is not 0, the receive circuits are reset and the unit goes back to looking for another 1-to-0 transition. This is to provide rejection of false start bits. If the start bit proves valid, it is shifted into the input shift register, and reception of the rest of the frame will proceed.

As data bits come in from the right, 1s shift out to the left. When the start bit arrives at the left-most position in the shift register, (which in mode 1 is a 9-bit register), it flags the RX Control block to do one last shift, loads S0BUF and RB8, and set RI. The signal to load S0BUF and RB8, and to set RI, will generated if, and only if, the

following conditions are met at the time the final shift pulse is generated.

- 1. R1 = 0, and

- 2. Either SM2 = 0, or the received stop bit = 1

If either of these two conditions is not met, the received frame is irretrievably lost. If both conditions are met, the stop bit goes into RB8, the 8 data bits go into S0BUF, and RI is activated. At this time, whether the above conditions are met or not, the unit goes back to looking for a 1-to-0 transition in RxD.

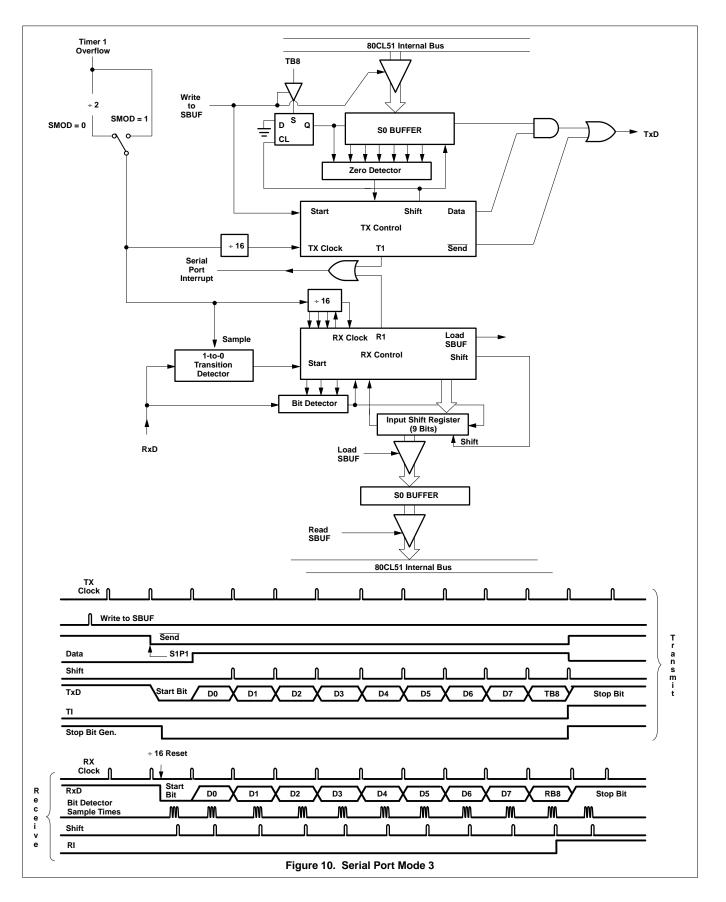

#### More about modes 2 and 3

Eleven bits are transmitted (through TxD), or received (through RxD): a start bit (0), 8 data bits (LSB first), a programmable 9th data bit, and a stop bit (1). On transmit, the 9th data bit (TB8) can be assigned the value of 0 or 1. On receive, the 9th data bit goes into RB8 in SCON. The baud rate is programmable to either 1/32 or 1/64 the oscillator frequency in Mode 2. Mode 3 may have a variable baud rate generated from Timer 1.

Figures 9 and 10 show a functional diagram of the serial port in Modes 2 and 3. The receive portion is exactly the same as in Mode 1. The transmit portion differs from Mode 1 only in the 9th bit of the transmit shift register.

Transmission is initiated by any instruction that uses S0BUF as a destination register. The "write to S0BUF" signal also loads TB8 into the 9th bit position of the transmit shift register and flags the TX Control unit that a transmission is requested. Transmission commences at S1P1 of the machine cycle following the next rollover in the divide-by-16 counter (thus, the bit times are synchronized to the divide-by-16 counter, not to the "write to S0BUF" signal). The transmission begins with activation of SEND, which puts the start bit at TxD. One bit time later, DATA is activated, which enables the output bit of the transmit shift register to TxD. One bit time later, DATA is activated, which enables the output bit of the transmit shift register to TxD. The first shift pulse occurs one bit time after that. The first shift clocks a 1 (the stop bit) into the 9th bit position of the shift register. Thereafter, only zeros are clocked in. Thus, as data bits shift out to the right, zeros are clocked in from the left. Then TB8 is at the output position of the shift register, then the stop bit is just to the left of TB8, and all positions to the left of that contains zeros. This condition flags the TX Control unit to do one last shift and then deactivate SEND and set TI. This occurs at the 11th divide-by-16 rollover after "write to S0BUF".

Reception is initiated by a detected 1-to-0 transition at RxD. For this purpose RxD is sampled at a rate of 16 times whatever baud rate has been established. When a transition is detected, the divide-by-16 counter is immediately reset, and 1FFFH is written to the input shift register.

At the 7th, 8th and 9th counter states of each bit time, the bit detector samples the value of RxD. The value accepted is the value that was seen in at least 2 of the 3 samples. If the value accepted during the first bit time is not 0, the receive circuits are reset and the unit goes back to looking for another 1-to-0 transition. If the start bit proves valid, it is shifted into the input shift register, and reception of the rest of the frame will proceed. As data bits come in from the right, 1s shift out to the left. When the start bit arrives at the left-most position in the shift register (which in Modes 2 and 3 is a 9-bit register), it flags the RX Control block to do one last shift, load S0BUF and RB8, and set RI.

### 80CL31/80CL51

The signal to load S0BUF and RB8, and to set RI, will be generated if, and only if, the following conditions are met at the time the final shift pulse is generated.

- 1. RI = 0, and

- 2. Either SM2 = 0 or the received 9th data bit = 1

If either of these conditions is not met, the received frame is irretrievably lost, and RI is not set. If both conditions are met, the received 9th data bit goes into RB8, and the first 8 data bits 90 into SOBUF. One bit time later, whether the above conditions were met or not, the unit goes back to looking for a 1-to-0 transition at the RxD input.

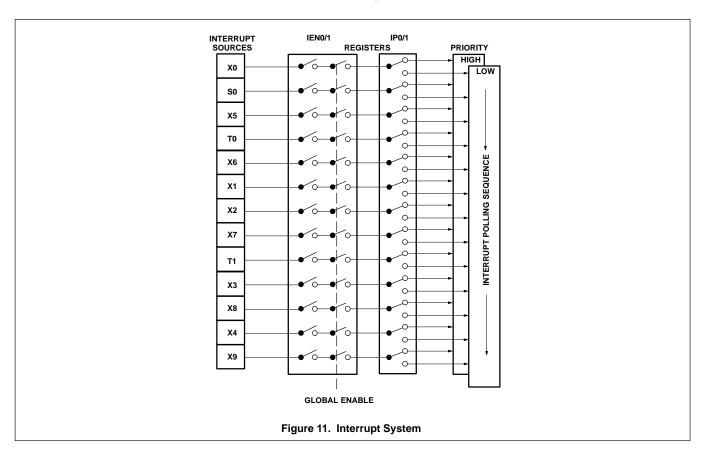

#### 1.6 Interrupt System

External events and the real-time-driven on-chip peripherals require service by the CPU asynchronous to do execution of any particular section of code. To tie the asynchronous activities of these functions to normal program execution, a multiple-source, two-priority-level, nested interrupt system is provided. The 80CL51 acknowledges interrupt requests from thirteen sources as follows:

- INT0 and INT1

- Timer 0 and Timer 1

- UART serial I/O

- INT2 to INT9 (Port 1)

Each interrupt vectors to a separate location in program memory for its service routine. Each source can be individually enabled or disabled by corresponding bits in the Interrupt Enable Registers (IE, IEO). The priority level is selected via the Interrupt Priority register (IP0, IP1). All enabled sources can be globally disabled or enabled.

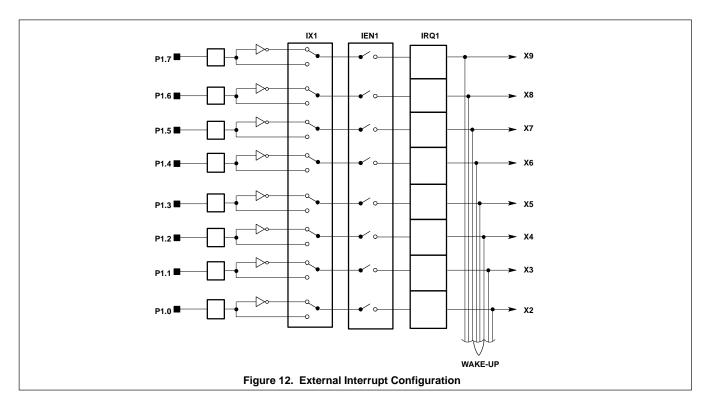

#### 1.6.1 External Interrupts INT2/INT9

Port 1 lines serve an alternative purpose as eight additional interrupts INT2 to INT9. When enabled, each of these lines may "wake-up" the device from Power-down mode. Using the IX1 register, each pin may be initialized to either active HIGH or LOW. IRQ1 is the interrupt request flag register. Each flag, if the interrupt is enabled, will be set on an interrupt request but must be cleared by software, i.e. via the interrupt software or when the interrupt is disabled.

The Port 1 interrupts are level sensitive. A Port 1 interrupt will be recognized when a level (HIGH or LOW depending on Interrupt Polarity Register IX1) on P1x is held active for at least one machine cycle. The Interrupt Request is not served until the next machine cycle.

### 80CL31/80CL51

#### Interrupt enable register IEN0, IEN1 IEN0 (A8H)

| EA       | -      | ES1       | ES0        | ET1       | EX1        | ET0       | EX0      |

|----------|--------|-----------|------------|-----------|------------|-----------|----------|

| Bit      | Symbol |           | Functio    | n         |            |           |          |

| IEN0.7   | EA G   | eneral er | nable/dis  | able con  | trol       |           |          |

|          | 0      | = no inte | rrupt is e | enabled   |            |           |          |

|          | 1      | = any ind | lividually | enabled   | l interrup | t will be | accepted |

| IEN0.6   | - U    | nused     |            |           |            |           |          |

| IEN0.5 E | ES1 U  | nused     |            |           |            |           |          |

| IEN0.4 E | ESO EI | nable UA  | RT SIO     | interrupt |            |           |          |

| IEN0.3 E | ET1 Ei | nable tim | er T1 int  | errupt    |            |           |          |

| IEN0.2 E | EX1 Ei | nable ext | ernal int  | errupt    |            |           |          |

| IEN0.1 E | ETO EI | nable Tin | ner T0 in  | terrupt   |            |           |          |

| IEN0.0 E | EX0 Ei | nable ext | ernal int  | errupt 0  |            |           |          |

|          |        |           |            |           |            |           |          |

#### IEN1 (E8H)

| <u> </u> | ,         |            |            |           |     |     |     |

|----------|-----------|------------|------------|-----------|-----|-----|-----|

| EX9      | EX8       | EX7        | EX6        | EX5       | EX4 | EX3 | EX2 |

| Bit      | Symbol    | -          | Functior   | า         |     |     |     |

| IEN1.7   | EX9       | Enable e   | external i | nterrupt  | 9   |     |     |

| IEN1.6   | EX8       | Enable e   | external i | nterrupt  | 8   |     |     |

| IEN1.5   | EX7       | Enable e   | external i | interrupt | 7   |     |     |

| IEN1.4   | EX6       | Enable e   | external i | nterrupt  | 6   |     |     |

| IEN1.3   | EX5       | Enable e   | external i | nterrupt  | 5   |     |     |

| IEN1.2   | EX4       | Enable e   | external i | nterrupt  | 4   |     |     |

| IEN1.1   | EX3       | Enable e   | external i | interrupt | 3   |     |     |

| IEN1.0   | EX2       | Enable e   | external i | interrupt | 2   |     |     |

| where 0  | = interru | int disahl | ed         |           |     |     |     |

where 0 = interrupt disabled

1 = interrupt enabled

Interrupt priority register IP0, IP1 IP0 (B8H)

| -                   | -      | PS1        | PS0        | PT1         | PX1  | PT0 | PX0 |  |  |

|---------------------|--------|------------|------------|-------------|------|-----|-----|--|--|

| Bit Symbol Function |        |            |            |             |      |     |     |  |  |

| IP0.7               | - U    | nused      |            |             |      |     |     |  |  |

| IP0.6               | - U    | nused      |            |             |      |     |     |  |  |

| IP0.5               | PS1 U  | nused      |            |             |      |     |     |  |  |

| IP0.4               | PS0 U  | ART SIO    | interrup   | t           |      |     |     |  |  |

| IP0.3               | PT1 Ti | mer 1 int  | errupt pr  | iority lev  | el   |     |     |  |  |

| IP0.2               | PX1 E  | xternal in | terrupt 1  | priority I  | evel |     |     |  |  |

| IP0.1               | PT0 Ti | mer 0 int  | errupt pr  | iority lev  | el   |     |     |  |  |

| IP0.0               | PX0 E  | xternal in | terrupt 0  | priority I  | evel |     |     |  |  |

| IP1 (B8             | BH)    | -          | -          | -           | -    | -   | -   |  |  |

| PX9                 | PX8    | PX7        | PX6        | PX5         | PX4  | PX3 | PX2 |  |  |

| Bit S               | Symbol |            | Functio    | n           |      |     |     |  |  |

| IP1.7               | PX9 Ex | ternal int | errupt 9 p | oriority le | evel |     |     |  |  |

| IP1.6               | PX8 Ex | ternal int | errupt 8 p | oriority le | evel |     |     |  |  |

| IP1.5               | PX7 Ex | ternal int | errupt 7 p | oriority le | evel |     |     |  |  |

| IP1.4               | PX6 Ex | ternal int | errupt 6 p | oriority le | evel |     |     |  |  |

IP1.3PX5External interrupt 5 priority levelIP1.2PX4External interrupt 4 priority level

IP1.1 PX3 External interrupt 3 priority level

IP1.0 PX2 External interrupt 2 priority level

Interrupt priority is as follows:

- 0 = low priority

- 1 = high priority

### 80CL31/80CL51

| Interrupt polarity register IX1 |  |

|---------------------------------|--|

| IX1 (E9H)                       |  |

|                                               | IL9                 | IL8 | IL7 | IL6 | IL5 | IL4 | IL3 | IL2 |  |  |

|-----------------------------------------------|---------------------|-----|-----|-----|-----|-----|-----|-----|--|--|

|                                               | Bit Symbol Function |     |     |     |     |     |     |     |  |  |

| IX1.7 IL9 External interrupt 9 polarity level |                     |     |     |     |     |     |     |     |  |  |

| IX1.6 IL8 External interrupt 8 polarity level |                     |     |     |     |     |     |     |     |  |  |

| IX1.5 | IL7 | External interrupt 7 polarity level |

|-------|-----|-------------------------------------|

| IX1.4 | IL6 | External interrupt 6 polarity level |

| IX1.3 | IL5 | External interrupt 5 polarity level |

| IX1.2 | IL4 | External interrupt 4 polarity level |

| IX1.1 | IL3 | External interrupt 3 polarity level |

| IX1.0 | IL2 | External interrupt 2 polarity level |

|       |     |                                     |

# Interrupt request flag register IRQ1 IRQ1 (C0H)

IRQ1.0 IQ2 External interrupt 2 request flag

|          | ••••                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                    |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                        |                         |                                                                                                                                                                                                                                                                                                    |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IQ9      | IQ8                                                                                                                                                                                            | IQ7                                                                                                                                                                                                                                                                                                      | IQ6                                                                                                                                                                                | IQ5                                                                                                                                                                                                                           | IQ4                                                                                                                                                                                                                                                                                    | IQ3                     | IQ2                                                                                                                                                                                                                                                                                                |

| Bit Sy   | /mbol                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                          | Functior                                                                                                                                                                           | า                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                        |                         |                                                                                                                                                                                                                                                                                                    |

| IRQ1.7 I | Q9 Exte                                                                                                                                                                                        | ernal inte                                                                                                                                                                                                                                                                                               | rrupt 9 re                                                                                                                                                                         | equest fla                                                                                                                                                                                                                    | ag                                                                                                                                                                                                                                                                                     |                         |                                                                                                                                                                                                                                                                                                    |

| IRQ1.6 I | Q8 Exte                                                                                                                                                                                        | ernal inte                                                                                                                                                                                                                                                                                               | rrupt 8 re                                                                                                                                                                         | equest fla                                                                                                                                                                                                                    | ag                                                                                                                                                                                                                                                                                     |                         |                                                                                                                                                                                                                                                                                                    |

| IRQ1.5 I | Q7 Exte                                                                                                                                                                                        | ernal inte                                                                                                                                                                                                                                                                                               | rrupt 7 re                                                                                                                                                                         | equest fla                                                                                                                                                                                                                    | ag                                                                                                                                                                                                                                                                                     |                         |                                                                                                                                                                                                                                                                                                    |

| IRQ1.4 I | Q6 Exte                                                                                                                                                                                        | ernal inte                                                                                                                                                                                                                                                                                               | rrupt 6 re                                                                                                                                                                         | equest fla                                                                                                                                                                                                                    | ag                                                                                                                                                                                                                                                                                     |                         |                                                                                                                                                                                                                                                                                                    |

| IRQ1.3 I | Q5 Exte                                                                                                                                                                                        | ernal inte                                                                                                                                                                                                                                                                                               | rrupt 5 re                                                                                                                                                                         | equest fla                                                                                                                                                                                                                    | ag                                                                                                                                                                                                                                                                                     |                         |                                                                                                                                                                                                                                                                                                    |

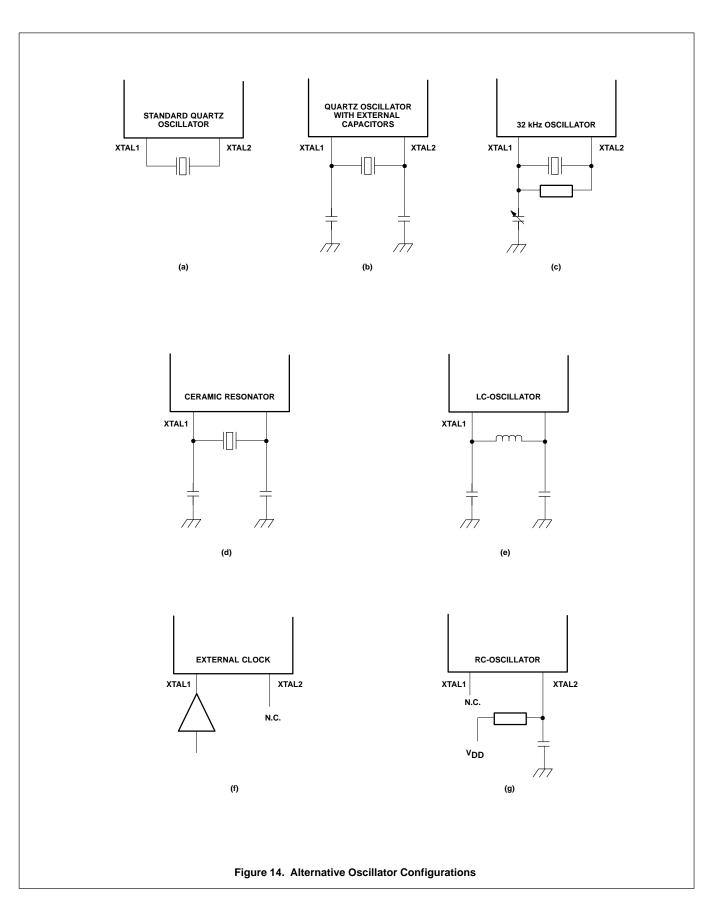

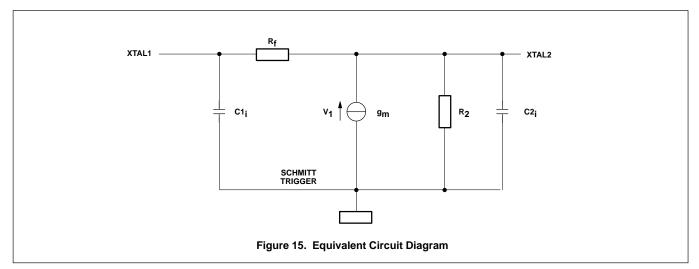

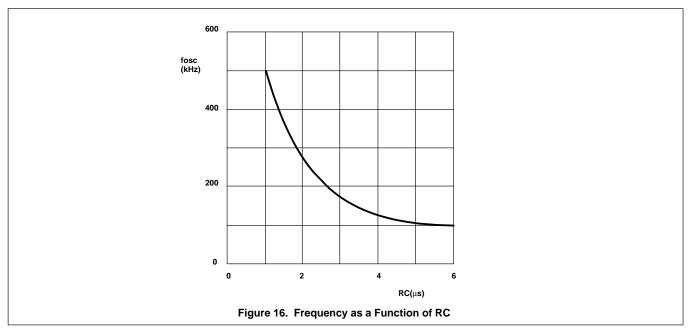

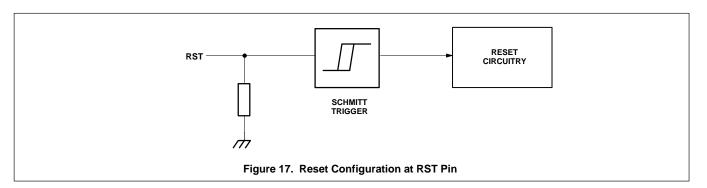

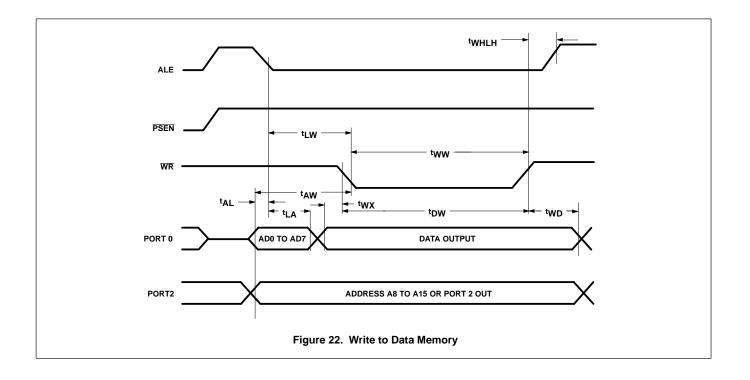

| IRQ1.2 I | Q4 Exte                                                                                                                                                                                        | ernal inte                                                                                                                                                                                                                                                                                               | rrupt 4 re                                                                                                                                                                         | equest fla                                                                                                                                                                                                                    | ag                                                                                                                                                                                                                                                                                     |                         |                                                                                                                                                                                                                                                                                                    |