# 54S/74S139 54LS/74LS139

**DUAL 1-OF-4 DECODER**

**DESCRIPTION** — The '139 is a high speed dual 1-of-4 decoder/demultiplexer. The device has two independent decoders, each accepting two inputs and providing four mutually exclusive active LOW outputs. Each decoder has an active LOW Enable input which can be used as a data input for a 4-output demultiplexer. Each half of the '139 can be used as a function generator providing all four minterms of two variables. The '139 is fabricated with the Schottky barrier diode process for high speed.

- SCHOTTKY PROCESS FOR HIGH SPEED

- MULTIFUNCTION CAPABILITY

- TWO COMPLETELY INDEPENDENT 1-OF-4 DECODERS

- ACTIVE LOW MUTUALLY EXCLUSIVE OUTPUTS

**ORDERING CODE:** See Section 9

|                    | PIN | COMMERCIAL GRADE                                                                         | MILITARY GRADE                                                                               | PKG  |  |  |

|--------------------|-----|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------|--|--|

| PKGS               | OUT | $V_{CC} = +5.0 \text{ V } \pm 5\%,$<br>$T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}$ | $V_{CC} = +5.0 \text{ V} \pm 10\%,$<br>$T_A = -55^{\circ}\text{ C to} +125^{\circ}\text{ C}$ | TYPE |  |  |

| Plastic<br>DIP (P) | Α   | 74S139PC, 74LS139PC                                                                      |                                                                                              | 9B   |  |  |

| Ceramic<br>DIP (D) | Α   | 74S139DC, 74LS139DC                                                                      | 54S139DM, 54LS139DM                                                                          | 6B   |  |  |

| Flatpak<br>(F)     | Α   | 74S139FC, 74LS139FC                                                                      | 54S139FM, 54LS139FM                                                                          | 4L   |  |  |

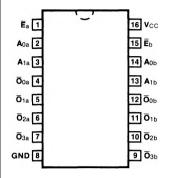

# CONNECTION DIAGRAM PINOUT A

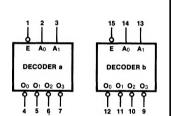

### LOGIC SYMBOL

V<sub>CC</sub> = Pin 16 GND = Pin 8

### INPUT LOADING/FAN-OUT: See Section 3 for U.L. definitions

| PIN NAMES                                                                                                | DESCRIPTION                                                   | <b>54/74S (U.L.)</b><br>HIGH/LOW  | 54/74LS (U.L.)<br>HIGH/LOW              |  |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------------------------------|-----------------------------------------|--|

| A <sub>0</sub> , A <sub>1</sub><br><del>E</del><br><del>O</del> <sub>0</sub> — <del>O</del> <sub>3</sub> | Address Inputs Enable Input (Active LOW) Outputs (Active LOW) | 1.25/1.25<br>1.25/1.25<br>25/12.5 | 0.5/0.25<br>0.5/0.25<br>10/5.0<br>(2.5) |  |

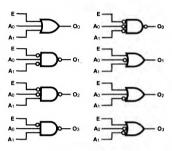

**FUNCTIONAL DESCRIPTION** — The '139 is a high speed dual 1-of-4 decoder/demultiplexer fabricated with the Schottky barrier diode process. The device has two independent decoders, each of which accepts two binary weighted inputs  $(A_0, A_1)$  and provides four mutually exclusive active LOW outputs  $(\overline{O}_0 - \overline{O}_3)$ . Each decoder has an active LOW enable  $(\overline{E})$ . When  $\overline{E}$  is HIGH all outputs are forced HIGH. The enable can be used as the data input for a 4-output demultiplexer application. Each half of the '139 generates all four minterms of two variables. These four minterms are useful in some applications, replacing multiple gate functions as shown in *Figure* a, and thereby reducing the number of packages required in a logic network.

**TRUTH TABLE**

| IN | IPUT:          | s              | OUTPUTS |                |    |    |  |

|----|----------------|----------------|---------|----------------|----|----|--|

| Ē  | A <sub>0</sub> | A <sub>1</sub> | ō       | Ō <sub>1</sub> | Ō₂ | Ō₃ |  |

| H  | Х              | Х              | Н       | Н              | Н  | Н  |  |

| L  | L              | L              | L       | Н              | Н  | Н  |  |

| L  | Н              | L              | Н       | L              | Н  | Н  |  |

| L  | L              | Н              | Н       | Н              | L  | Н  |  |

| L  | Н              | Н              | Н       | Н              | Н  | L  |  |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

Fig. a

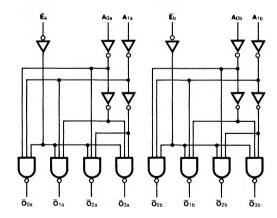

#### **LOGIC DIAGRAM**

## DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwisespecified)

| SYMBOL | PARAMETER            |     | 54/74LS |     | 748 | UNITS | CONDITIONS            |

|--------|----------------------|-----|---------|-----|-----|-------|-----------------------|

|        |                      | Min | Max     | Min | Max |       |                       |

| lcc    | Power Supply Current |     | 11      |     | 90  | mA    | V <sub>CC</sub> = Max |

## AC CHARACTERISTICS: $V_{CC} = +5.0 \text{ V}$ , $T_A = +25^{\circ} \text{C}$ (See Section 3 for waveforms and load configurations)

|                                      |                                                      | 54/74LS |                        | 54/74\$ |                |       | CONDITIONS          |

|--------------------------------------|------------------------------------------------------|---------|------------------------|---------|----------------|-------|---------------------|

| SYMBOL                               | PARAMETER                                            |         | C <sub>L</sub> = 15 pF |         | 15 pF<br>280 Ω | UNITS |                     |

|                                      |                                                      | Min     | Max                    | Min     | Max            |       |                     |

| tpLH<br>tpHL                         | Propagation Delay $A_0$ or $A_1$ to $\overline{O}_n$ |         | 18<br>27               |         | 12<br>12       | ns    | Figs. 3-1, 3-4, 3-5 |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay E to On                            |         | 15<br>24               |         | 8.0<br>10      | ns    | Figs. 3-1, 3-5      |