## 54/74290 54LS/74LS290

### **BCD DECADE COUNTER**

**DESCRIPTION** — The '290 is a 4-stage ripple counter containing a high speed flip-flop acting as a divide-by-two and three flip-flops connected as a divide-by-five. HIGH signals on the Master Reset (MR) inputs override the clocks and force all outputs to the LOW state. HIGH signals on the Master Set (MS) inputs override the clocks and MR and force the outputs to the BCD nine state. The '290 is the same circuit as the '90 except that it has corner power pins and is therefore recommended for new designs. For detail specifications, truth tables and functional description, please refer to the '90 data sheet.

#### **ORDERING CODE:** See Section 9

|                    | PIN | COMMERCIAL GRADE                                                                         | GRADE MILITARY GRADE                                                                        |             |  |

|--------------------|-----|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------|--|

| PKGS               | ОПТ | $V_{CC} = +5.0 \text{ V } \pm 5\%,$<br>$T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}$ | $V_{CC} = +5.0 \text{ V} \pm 10\%,$<br>$T_A = -55^{\circ}\text{C to} + 125^{\circ}\text{C}$ | PKG<br>TYPE |  |

| Plastic<br>DIP (P) | A   | 74290PC, 74LS290PC                                                                       |                                                                                             | 9A          |  |

| Ceramic<br>DIP (D) | A   | 74290DC, 74LS290DC                                                                       | 54290DM, 54LS290DM                                                                          | 6A          |  |

| Flatpak<br>(F)     | А   | 74290FC, 74LS290FC                                                                       | 54290FM, 54LS290FM                                                                          | 31          |  |

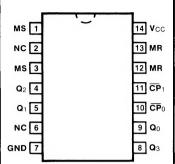

# CONNECTION DIAGRAM PINOUT A

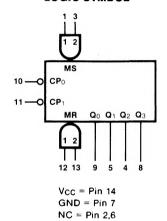

### LOGIC SYMBOL

### INPUT LOADING/FAN-OUT: See Section 3 for U.L. definitions

| PIN NAMES                         | DESCRIPTION                                             | <b>54/74 (U.L.)</b><br>HIGH/LOW | 54/74LS (U.L.)<br>HIGH/LOW<br>1.0/1.5 |  |

|-----------------------------------|---------------------------------------------------------|---------------------------------|---------------------------------------|--|

| CP <sub>0</sub>                   | ÷2 Section Clock Input<br>(Active Falling Edge)         | 2.0/2.0                         |                                       |  |

| CP <sub>1</sub>                   | ÷5 Section Clock Input (Active Falling Edge)            | 3.0/3.0                         | 2.0/2.0                               |  |

| MR <sub>1</sub> , MR <sub>2</sub> | Asynchronous Master Reset<br>Inputs (Active HIGH)       | 1.0/1.0                         | 0.5/0.25                              |  |

| MS <sub>1</sub> , MS <sub>2</sub> | Asynchronous Master Set (Set to 9) Inputs (Active HIGH) | 1.0/1.0                         | 0.5/0.25                              |  |

| Q <sub>0</sub>                    | ÷2 Flip-flop Output*                                    | 20/10                           | 10/5.0<br>(2.5)                       |  |

| Q <sub>1</sub> — Q <sub>3</sub>   | ÷5 Flip-flop Outputs                                    | 20/10                           | 10/5.0<br>(2.5)                       |  |

<sup>\*</sup>The Q<sub>0</sub> output is guaranteed to drive the full rated fan-out plus the CP<sub>1</sub> input.