# National Semiconductor

## 2470A Servo Demodulator

#### **General Description**

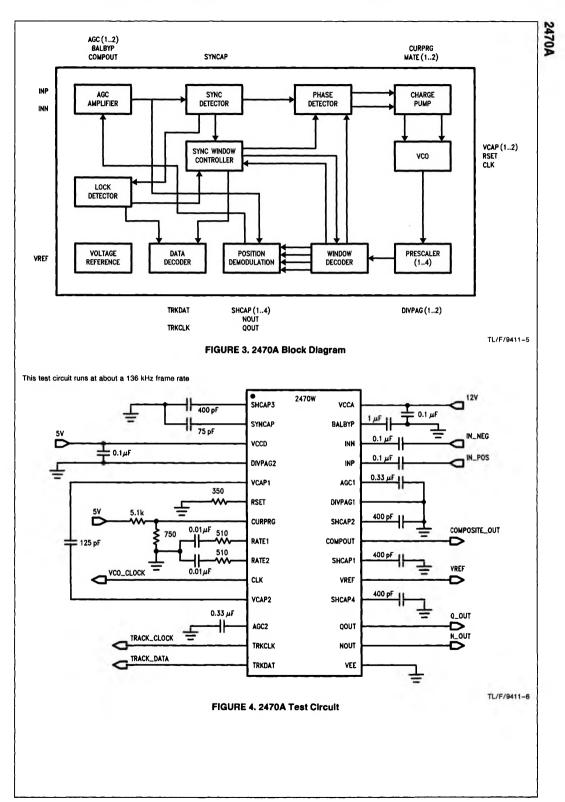

The new 2470A servo demodulator decodes the quadrature di-bit pattern from the dedicated servo surface providing position and data information.

#### Features

- Quadrature positions signals

- Phase locked to servo pattern with embedded lock indication

- Track data and track clock for data encoding

- AGC amplifier with 36 dB range

- Servo fields to 400 kHz

- Compatible with the 24H80 servo preamp and 2460 servo control chip

- Standard 5V and 12V supplies

- New phase detector eliminates jitter due to dropped sync's

# For most current package information, contact product marketing.

New lock detector uses sync pulse location to determine sync. Dropped pulses are not out of sync conditions.

2470A

- New ±20% VCO with extended frequency capability (>30 MHz)

- New totem pole TTL outputs

- New sync detector eliminates one shot multivibrator settina

- New sample and hold circuits eliminate output droop and alitching of the guadrature circuits

- New reference centers the guadrature outputs in the 12V supply

- New sync window controller prevents erroneous pulses from reaching the phase detector for a second level of iitter prevention

28 27

10

25 INF

24

23

22

21

20

19

AGC1

DIVPAG1

SHCAP2

COMPOUT

SHCAP1

TL/F/9411-2

VREF

#### **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications. -65°C to +175°C Storage Temperature

Lead Temperature Ceramic DIP (10 sec.) 300°C Internal Power Dissipation 2.5W Supply Voltage V<sub>CCD</sub> Supply Voltage V<sub>CCA</sub>

6V

15V

#### **Operating Temperature**

#### **2470A Electrical Specification** $T_A = 25^{\circ}C$ , $V_{CCD} = 5V$ , $V_{VCCA} = 12V$

0°C to + 70°C

| Parar                                 | neter                         | Conditions                                 | Min             | Тур                          | Max              | Units      |

|---------------------------------------|-------------------------------|--------------------------------------------|-----------------|------------------------------|------------------|------------|

| AGC AMPLIF                            | IER                           |                                            |                 |                              |                  |            |

| Max Voltage G                         | ain                           | Input Freq. = 1 MHz                        | 40              | 46                           |                  | dB         |

| AGC Range                             |                               | Input Freq. = 1 MHz                        | 20              | 36                           |                  | dB         |

| Frequency Re                          | sponse                        |                                            |                 | 10                           |                  | MHz        |

| Input Voltage                         | Range                         | 0                                          | 30              |                              | 300              | mV         |

| Output Voltag                         |                               |                                            | 3.0             | 3.3                          | 3.6              | VPP        |

| Common Mod                            | e Voltage                     |                                            | l               | 8.2                          | 1                | V          |

| QUADRATUP                             | RE OUTPUTS (Refe              | erred to 6V ref; $R_L \approx 20k$ )       |                 |                              |                  |            |

| Output Voltag                         | e                             | R <sub>L</sub> = 20k                       | 3.0             | 3.3                          | 3.6              | Vpp        |

| Output Imped                          | ance                          |                                            | 1               |                              | 100              | Ω          |

| Output Offset                         | Voltage                       |                                            |                 | ±5                           | + 20             | mV         |

| Output Curren                         | it                            | (Note: Out Impedance)                      |                 | 5                            | 6                | mA         |

| VOLTAGE RE                            | FERENCE                       |                                            | <u></u>         |                              |                  |            |

| Output Voltag                         | e                             |                                            | 5.88            | 6.00                         | 6.12             | v          |

| Output Curren                         | nt                            |                                            |                 | 5                            | 6                | mA         |

| V <sub>CO</sub>                       |                               |                                            |                 |                              |                  |            |

| Max Frequenc                          | cy V <sub>CO</sub> (Ctr)      |                                            |                 | 30                           |                  | MHz        |

| PLL System                            | Performance using             | g sine <sup>3</sup> Waveform as Servo Refe | erence. Frame(c | enter) = V <sub>CO</sub> (ce | enter)/divider r | atio.      |

| Acquisition Ra                        | ange                          |                                            | ±10%            | ±15%                         |                  | frame(ctr) |

| Dropped Sync                          | Endurance                     |                                            | 15              | 40                           | -                | frames     |

| Maximum Fra                           | me Rate                       |                                            | 400             |                              |                  | kHz        |

| LOGIC                                 |                               |                                            |                 |                              |                  |            |

| Input Voltage                         | Low                           |                                            |                 |                              | 0.8              | v          |

| Input Voltage                         | High                          |                                            | 2.0             |                              | 1                | V          |

| Output Voltag                         | e Low                         |                                            |                 |                              | 0.5              | V V        |

| Output Voltag                         | e High                        |                                            | 2.7             |                              |                  | V          |

| Risetime                              |                               | 10%-90%                                    |                 | 9                            | 20               | ns         |

| Falltime                              |                               | 10%-90%                                    |                 | 4                            | 14               | ns         |

| DIVIDER TAE                           | BLE Ratio = V <sub>CO</sub> F | Frequency + Frame Rate                     |                 |                              |                  |            |

| DIVPAG1                               | DIVPAG2                       | RATIO                                      |                 |                              |                  |            |

| 0                                     | 0                             | 32                                         |                 |                              |                  |            |

| 1                                     | 0                             | 64                                         |                 |                              |                  |            |

| 0                                     | 1                             | 96                                         |                 |                              |                  | ł          |

| 1                                     | 1                             | 128                                        | 1               |                              |                  |            |

|                                       | Ratings                       |                                            |                 |                              |                  |            |

| Power Supply                          |                               |                                            | -               | 80                           | 100              | mA         |

| Power Supply<br>V <sub>CCD</sub> (5V) |                               |                                            |                 |                              |                  |            |

#### Features of the 2470A Servo Demodulator

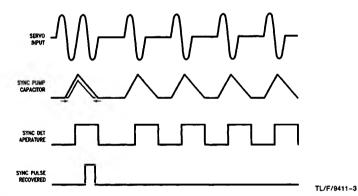

- The sync detecting operation is based on the servo disk's own timing and eliminates the need to precisely set a resistor-capacitor time constant for the di-bit detecting one shot timer. The new circuit uses a single low precision capacitor.

- 2) The phase detector has a linear phase vs. output detection scheme as an improvement over the one shot scheme. The circuit performs no detection for dropped sync pulses and when in lock as defined by the lock detector, it will only detect in a predefined window. These features eliminate jitter caused by dropped pulses and/or bad servo areas on the disk. Also eliminated are the phase detector external components.

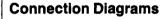

Out of lock conditions require acquisition aids to achieve lock. Should a sync pulse show outside the sync window (2 of 32 counts in a servo field), aperature control circuits realign the sync pulse with the sync window by resetting the decoder and enlarge the next window to find a sync pulse with the VCO's  $\pm$  20% tuning range. The limited range on the VCO prevents 2X locks. The aperature control prevents the dropped pulse ignoring phase detector from achieving non-integral false locks. The window realignment and enlargement is disabled during lock to prevent erroneous sync pulses from upsetting the decoder.

3) The new lock detector ignores dropped pulses in testing for in and out of lock conditions. Should a sync pulse appear the detector records whether or not it appeared in the normal sync window. The lock detector uses four consecutive sync pulses either all out or all in the sync window to determine lock status. The lock detector enables and disables the aperature control for the phase detector and the sync data detector. 24704

- 4) The 2470A has a VCO with improved performance. It has > 30 MHz operation and a restricted tuning range of ±20%. Tuning circuits will reduce jitter due to parasitic couplings into the VCO.

- 5) New sample hold circuits for the N and Q decoders eliminate the droop in the N and Q outputs. The sample holds are opened immediately after the peak detection is complete. This eliminates droop induced offsets and glitching.

- TTL totem pole outputs eliminates the need for resistive pullup for the output. Switching times of 10 ns are achieved.

- 7) The analog reference is 6V. Centering in the 12V supply lines is easier. The 6V reference maintains compatibility with the 2460 servo controller and the 24H80 preamp.

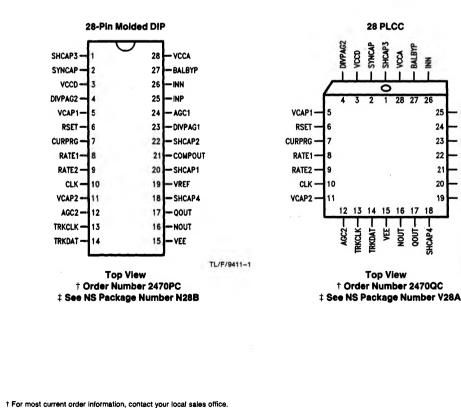

| Lead         | Name             | Function                                  |  |

|--------------|------------------|-------------------------------------------|--|

| NPUT SIGNALS |                  |                                           |  |

| 23           | DIVPAG1          | Programs the prescaler for the VCO        |  |

| 4            | DIVPAG2          | Divide ratios are 32, 64, 96 and 128      |  |

| 7            | CURPRG           | Voltage sets PLL charge pump bias current |  |

| 15           | V <sub>EE</sub>  | Ground 0V                                 |  |

| 3            | V <sub>CCD</sub> | + 5V supply                               |  |

| 28           | VCCA             | + 12V supply                              |  |

| 25           | INP              | Composite inputs to the AGC amplifier     |  |

| 26           | INN              |                                           |  |

| DUTPUTS      |                  |                                           |  |

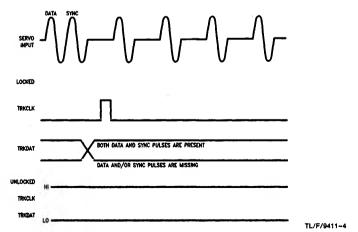

| 13           | TRKCLK           | Clock output for data during lock, TTL    |  |

| 14           | TRKDAT           | Data from dropped sync pulses TTL         |  |

| 10           | CLK              | VCO output TTL                            |  |

| 21           | COMPOUT          | Output of AGC amplifier @8.2V CM          |  |

| 19           | V <sub>REF</sub> | 6V reference for N and Q outputs          |  |

| 16           | NOUT             | Normal position signal @6V CM             |  |

| 17           | Q <sub>OUT</sub> | Quadrature position signal @6V CM         |  |

### List of Lead Functions

| Lead             | Name                   | Function                                                                                                                                       |

|------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTERNAL COMPO   | NENTS                  |                                                                                                                                                |

| 2                | SYNCAP                 | Timing capacitor for the sync detector                                                                                                         |

| 5-11             | V <sub>CAP</sub> 1 & 2 | VCO timing capacitor                                                                                                                           |

| 8-9              | Rate 1 & 2             | PLL loop filter                                                                                                                                |

| 27               | BALBYP                 | DC offset restore filter capacitor.                                                                                                            |

| 24               | AGC1                   | AGC system loop filter                                                                                                                         |

| 12               | AGC2                   | AGC2 Pin includes an amplitude control function. This pin<br>has a nominal voltage of 5V. The amplitude increases<br>according to the formula: |

|                  |                        | $\frac{V_{(COMPOUT P-P)} - V_{(COMPOUT NOM P-P)}}{V_{(AGC2)} - V_{(AGC2 NOM)}} = -0.7$ AGC2 is Pin 12 and COMPOUT is Pin 21.                   |

| 6                |                        | Sets the VCO bias currents I < 2 mA                                                                                                            |

|                  | R <sub>SET</sub>       |                                                                                                                                                |

| 20, 22,<br>1, 18 | SHCAP 14               | Four sample hold capacitors                                                                                                                    |

The sync pulse gate is triggered by the sync det aperature and is locked open until the sync goes to zero. The locking mechanism prevents clipping the negative edge of the sync.

#### FIGURE 1. Sync Detector Diagram

FIGURE 2. Track Data Output Information