1103-I,N

1103

#### DESCRIPTION

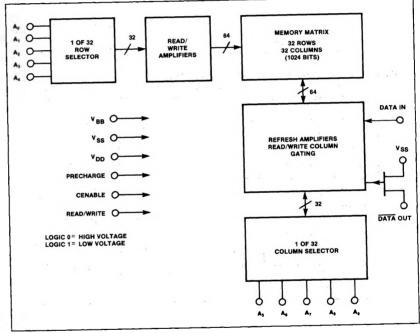

The 1103 is designed for main memory applications where high performance, low cost and large bit storage are important design objectives. It is a random access memory element using enhancement mode p-channel MOS devices integrated on a monolithic array. It is fully decoded, permitting the use of an 18-pin dual in-line package. The dynamic circuitry dissipates significant power only during precharge. Information stored in the memory is nondestructively read. Refreshing of all 1024 bits is accomplished in 32 read cycles and is required every 2ms. A separate cenable (chip enable) lead allows easy selection of an individual package when outputs are OR-tied. Use Signetics 8T25 sense amp, and 3207 clock driver.

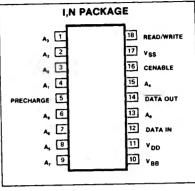

#### **PIN CONFIGURATION**

#### **BLOCK DIAGRAM**

### **ABSOLUTE MAXIMUM RATINGS1**

|                  | PARAMETER                                                                                                               | RATING                                   | UNIT         |

|------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------------|

| TA<br>Tstg<br>PD | Temperature range<br>Operating<br>Storage<br>Power dissipation<br>All input or output                                   | 0 to 70<br>-65 to 150<br>1<br>-25 to 0.3 | °C<br>W<br>V |

|                  | voltages with respect to the most<br>positive supply voltage, VBB<br>Supply voltages VDD and VSS<br>with respect to VBB | -25 to 0.3                               | v            |

1103-I,N

1103

####

| PARAMETER           |                                       | TEST CONDITIONS                           | Min Typ              |     | Max                    | UNIT |  |

|---------------------|---------------------------------------|-------------------------------------------|----------------------|-----|------------------------|------|--|

|                     | Input voltage                         |                                           |                      |     | 1                      | v    |  |

|                     | Low                                   |                                           |                      |     |                        |      |  |

| VIL1 <sup>4</sup>   | All address and data in lines         | $T_A = 0^{\circ}C$                        | Vss - 17             |     | Vss - 14.2             |      |  |

| VIL2 <sup>4</sup>   | All address and data in lines         | T <sub>A</sub> = 70° C                    | V <sub>SS</sub> - 17 |     | Vss - 14.5             |      |  |

| VIL34,5             | Precharge, Cenable, Read/write inputs | $T_A = 0^\circ C$                         | Vss - 17             |     | Vss - 14.7             |      |  |

| VIL4 <sup>4,5</sup> | Precharge, Cenable, Read/write inputs | $T_A = 70^{\circ}C$                       | Vss - 17             |     | V <sub>SS</sub> - 15.0 |      |  |

|                     | High <sup>4</sup>                     |                                           |                      |     |                        |      |  |

| VIH1                | All inputs                            | $T_A = 0^{\circ}C$                        | Vss - 1              |     | Vss + 1                |      |  |

| VIH2                | All inputs                            | T <sub>A</sub> = 70° C                    | Vss - 0.7            |     | Vss + 1                |      |  |

|                     | Output voltage                        | $R_{LOAD} = 100\Omega^6$                  | {                    |     |                        | mV   |  |

| Vol                 | Low <sup>7</sup>                      |                                           | 1                    |     | 1                      |      |  |

|                     | High                                  |                                           |                      |     |                        |      |  |

| VoH1                |                                       | T <sub>A</sub> = 25°C                     | 60                   | 90  | 400                    |      |  |

| VOH2                |                                       | $T_A = 70^{\circ}C$                       | 50                   | 80  | 400                    |      |  |

|                     | Supply current                        | $T_A = 25^{\circ}C$ , All addresses = 0V, |                      |     |                        | mA   |  |

|                     |                                       | Precharge = 0V                            |                      |     |                        |      |  |

| IDD1                | During TPC <sup>8</sup>               | Cenable = V <sub>SS</sub>                 |                      | 37  | 56                     |      |  |

| IDD2                | During Tov <sup>8</sup>               | Cenable = 0V                              |                      | 38  | 59                     |      |  |

| IDD3                | During TPOV <sup>8</sup>              | Cenable = 0V                              | 1 1                  | 5.5 | 11                     |      |  |

| IDD4                | During T <sub>CP</sub> 8              | Cenable = V <sub>SS</sub>                 | 1 1                  | 3   | 4                      |      |  |

| IDDAV               | Average <sup>9</sup>                  | Cycle time = 580ns,                       |                      | 17  | 25                     |      |  |

|                     |                                       | Precharge width = 190ns                   |                      |     |                        |      |  |

| IBB                 | VBB supply current                    |                                           |                      |     | 100                    | μA   |  |

|                     | Output current                        | $R_{LOAD} = 100\Omega^6$                  |                      |     |                        | μA   |  |

|                     | High                                  |                                           |                      |     |                        |      |  |

| IOH1                |                                       | T <sub>A</sub> = 25° C                    | 600                  | 900 | 4000                   |      |  |

| IOH2                |                                       | T <sub>A</sub> = 70°C                     | 500                  | 800 | 4000                   |      |  |

|                     | Capacitance <sup>10</sup>             | f = 1MHz, All unused pins are at          |                      |     |                        | pF   |  |

|                     |                                       | ac ground, VIN = VSS                      |                      |     |                        |      |  |

| CAD                 | Address                               | <b>0 00</b>                               |                      |     | 7                      |      |  |

| CPR                 | Precharge                             |                                           |                      |     | 18                     |      |  |

| CCE                 | Cenable                               |                                           |                      |     | 18                     |      |  |

| CRW                 | Read/write                            |                                           |                      |     | 15                     |      |  |

|                     | Data input                            |                                           |                      |     |                        |      |  |

| CIN1                |                                       | Cenable = 0V                              |                      |     | 5                      |      |  |

| CIN2                |                                       | Cenable = V <sub>SS</sub>                 |                      |     | 4                      |      |  |

|                     | Data output                           |                                           |                      |     |                        |      |  |

| COUT                |                                       | Vout = 0V                                 | 1 1                  |     | 3                      |      |  |

1103-I,N

1103

|                          |                                                             |                      |                                  |                                                                                                                                                                                 | LIMITS     |       |            | UNIT     |

|--------------------------|-------------------------------------------------------------|----------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|------------|----------|

| PARAMETER                |                                                             | то                   | FROM                             | TEST CONDITIONS                                                                                                                                                                 |            | Тур   | Max        |          |

| READ, W                  | RITE AND READ/WRITE CYCLE                                   |                      |                                  |                                                                                                                                                                                 |            |       |            |          |

| TREF                     | Time between refresh                                        |                      |                                  | 0                                                                                                                                                                               |            |       | 2          | ms       |

| tac                      | Setup and hold time<br>Setup time <sup>11</sup>             | Cenable              | Address                          |                                                                                                                                                                                 | 115        |       |            | ns       |

| tCA                      | Hold time                                                   | Address              | Cenable                          |                                                                                                                                                                                 | 20         |       |            |          |

| tPC <sup>11</sup><br>tCP | Delay time                                                  | Cenable<br>Precharge | Precharge<br>Cenable             |                                                                                                                                                                                 | 125<br>85  |       |            | ns       |

| tovL<br>tovн             | Precharge and cenable<br>overlap<br>Low<br>High             |                      |                                  | t = 20ns                                                                                                                                                                        | 25         |       | 75<br>140  | ns       |

| tovm                     | 50% points                                                  |                      |                                  |                                                                                                                                                                                 | 45         |       | 95         |          |

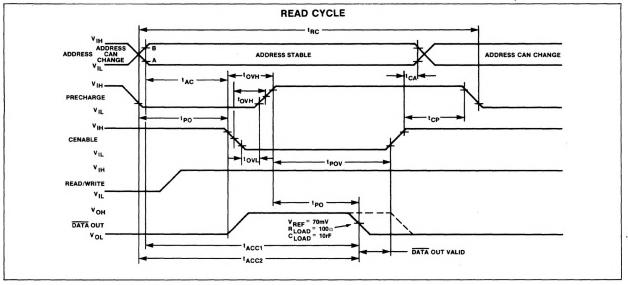

|                          | READ CYCLE                                                  |                      |                                  | $ \begin{array}{l} tAC(min) + tOVL(min + tPO(max) = \\ 2t, tPC(min) + tOVL(min) + tPO(max) \\ + 2t, t = 20ns, C_{LOAD} = 100pF, \\ R_{LOAD} = 100, V_{REF} = 40mV \end{array} $ |            |       |            | ~        |

| tRC                      | Read cycle11                                                |                      |                                  |                                                                                                                                                                                 | 480        |       |            | ns       |

|                          | Delay time                                                  |                      |                                  |                                                                                                                                                                                 | <u> </u>   |       | - 1        | ns       |

| tPOV                     |                                                             | End of<br>cenable    | Precharge                        |                                                                                                                                                                                 | 165        |       | 500        |          |

| tp0                      |                                                             | Output               | End of<br>precharge              |                                                                                                                                                                                 |            |       | 120        |          |

| tACC1                    | Access time11                                               | Output               | Address                          |                                                                                                                                                                                 | 300        |       |            | ns       |

| tACC2                    |                                                             | Output               | Precharge                        |                                                                                                                                                                                 | 310        |       |            |          |

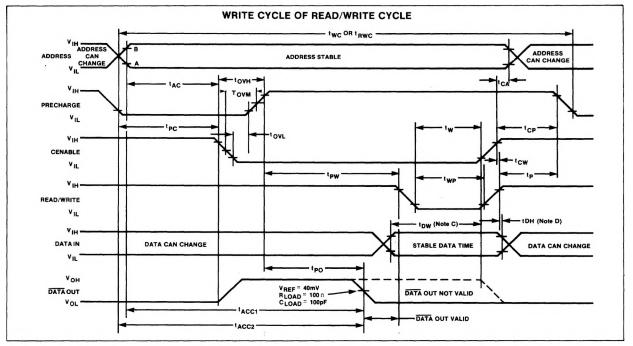

| WRITE                    | OR READ/WRITE CYCLE                                         |                      |                                  | $C_{LOAD} = 100 pF, R_{LOAD} = 100, V_{REF} = 40 mW$                                                                                                                            |            |       |            |          |

| twc<br>trwc              | Write cycle <sup>11</sup><br>Read/write cycle <sup>11</sup> |                      |                                  | t = 20ns<br>t = 20ns                                                                                                                                                            | 580<br>580 |       |            | ns<br>ns |

|                          | Delay time                                                  |                      |                                  |                                                                                                                                                                                 |            |       |            | ns       |

| tpw<br>tpo               |                                                             | Read/write<br>Output | Precharge<br>End of<br>precharge |                                                                                                                                                                                 | 165        | -0    | 500<br>120 |          |

|                          | Setup and hold time                                         |                      |                                  |                                                                                                                                                                                 | 1          |       |            | ns       |

| tw                       | Setup time                                                  | Chip enable<br>high  | Read/write                       |                                                                                                                                                                                 | 80         | - 10  |            |          |

| tow                      | Setup time                                                  | Chip enable<br>high  | Data                             |                                                                                                                                                                                 | 105        | - (c. |            |          |

| tDH .                    | Hold time                                                   | Data                 | R/W high                         |                                                                                                                                                                                 | 10         |       |            |          |

| tcw                      | Hold time                                                   | R/W high             | Chip enable<br>high              |                                                                                                                                                                                 |            |       | 10         |          |

| twp<br>tp                | Read/write pulse width<br>Time to next precharge            |                      |                                  |                                                                                                                                                                                 | 50<br>0    |       |            | ns<br>ns |

#### AC ELECTRICAL CHARACTERISTICS $T_A = 0^{\circ}C$ to $70^{\circ}C$ , $V_{SS} = 16 \pm 5\%$ , $(V_{BB} - V_{SS}) = 3.0V$ to 4.0V, $V_{DD} = 0V$

NOTES

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

2. The Vss current drain is equal to (IDD + IOH) or (IDD + IOL).

3. (VBB - VSS) supply should be applied at or before VSS.

- 4. The maximum values for V<sub>IL</sub> and the minimum values for V<sub>IH</sub> are linearly related to temperature between 0°C and 70°C. Thus any value in between 0°C and 70°C can be calculated by using a straight-line relationship.

- 5. The maximum values for V<sub>IL</sub> (for precharge, cenable and read/write) may be increased to Vss 14.2 at 0°C and Vss 14.5 at 70°C (same values as those specified for the address and data-in lines) with a 40ns degradation (worst case) in t<sub>AC</sub>, t<sub>PC</sub>, t<sub>RC</sub>, t<sub>WC</sub>, t<sub>RWC</sub>, t<sub>ACC</sub>; and t<sub>ACC</sub>.

6. This value of load resistance is used for measurement purposes. In applications the resistance may range from 100 $\Omega$  to 1k $\Omega.$

- 7. The output current when reading a low output is the leakage current of the 1103 plus external noise coupled into the output line from the clocks. VoL equals  $I_{OL}$  across the load resistor.

- 8. See Supply Current vs Temperature for guaranteed current at the temperature extremes. These values are taken from a single pulse measurement.

- 9. This parameter is periodically sampled and is not 100% tested.

- 10. This parameter is periodically sampled and is not 100% tested. It is measured at worst case operating conditions. Capacitance measurements for plastic package only.

- These times will degrade by 40ns (worst case) if the maximum values for V<sub>L</sub> (for precharge, cenable and read/write inputs) go to V<sub>SS</sub> – 14.2V at 0° C and V<sub>SS</sub> – 14.5V at 70° C.

1103-I,N

1103

#### TIMING DIAGRAMS

NOTES

A.  $V_{DD}$  + 2V B.  $V_{SS}$  - 2V  $$t_{\rm T}$ is defined as the transitions between these two points.$

C. tow is referenced to point 1 of the rising edge of cenable of read/write whichever occurs first.

D. t<sub>DH</sub> is referenced to point 2 of the rising edge of cenable or read/write whichever occurs first.